# FOR MORE EXCLUSIVE

# (Civil, Mechanical, EEE, ECE) ENGINEERING & GENERAL STUDIES

## (Competitive Exams)

TEXT BOOKS, IES GATE PSU's TANCET & GOVT EXAMS NOTES & ANNA UNIVERSITY STUDY MATERIALS

# VISIT

# www.EasyEngineering.net

AN EXCLUSIVE WEBSITE FOR ENGINEERING STUDENTS & GRADUATES

**\*\*Note:** Other Websites/Blogs Owners Please do not Copy (or) Republish this Materials without Legal Permission of the Publishers.

\*\*Disclimers : EasyEngineering not the original publisher of this Book/Material on net. This e-book/Material has been collected from other sources of net.

Downloaded From : www.EasyEngineering.net

Downloaded From : www.EasyEngineering.net

## First Edition : 2007-2008

TECHNICAL PUBLICATIONS

# Microprocessor & Microcontroller System

A. P. Godse D. A. Godse

**Technical Publications Pune**<sup>®</sup>

Downloaded From : www.EasyEngineering.net

# Apprise Education, Reprise Innovations

Copyrighted material Downloaded From : www.EasyEngineering.net

#### A. P. Godse

M. S. Software Systems (BITS Pilani) B.E. Industrial Electronics Formerly Lecturer in Department of Electronics Engg. Vishwakarma Institute of Technology Pune

#### Mrs. D. A. Godse

B.E. Industrial Electronics, M. E. (Computer) Assistant Professor in Bharati Vidyapeeth's Women's College of Engineering Pune

#### Visit us at : www.vtubooks.com

Technical Publications Pune

### Microprocessor and Microcontroller System

ISBN 978-81-8431-307-9

All rights reserved with Technical Publications. No part of this book should be reproduced in any form, Electronic, Mechanical, Photocopy or any information storage and retrieval system without prior permission in writing, from Technical Publications, Pune.

Published by :

Technical Publications Pune<sup>®</sup> #1, Amit Residency, 412, Shaniwar Peth, Pune - 411 030, India.

Printer :

Alert DTPrinters Sr.no. 10/3,Sinhagad Road, Pune - 411 041

> Copyrighted material Downloaded From : www.EasyEngineering.net

# Preface

The importance of **Microprocessor and Microcontroller System** is well known in various engineering fields. Overwhelming response to our books on various subjects inspired us to write this book. The book is structured to cover the key aspects of the subject Microprocessor and Microcontroller System.

The book uses plain, lucid language to explain fundamentals of this subject. The book provides logical method of explaining various complicated concepts and stepwise methods to explain the important topics. Each chapter is well supported with necessary illustrations, practical examples and solved problems. All the chapters in the book are arranged in a proper sequence that permits each topic to build upon earlier studies. All care has been taken to make students comfortable in understanding the basic concepts of the subject.

The book not only covers the entire scope of the subject but explains the philosophy of the subject. This makes the understanding of this subject more clear and makes it more interesting. The book will be very useful not only to the students but also to the subject teachers. The students have to omit nothing and possibly have to cover nothing more.

We wish to express our profound thanks to all those who helped in making this book a reality. Much needed moral support and encouragement is provided on numerous occasions by our whole families. We wish to thank the **Publisher** and the entire team of **Technical Publications** who have taken immense pain to get this book in time with quality printing.

Any suggestion for the improvement of the book will be acknowledged and well appreciated.

Authors

A. P. Godse D. A. Godse

Dedicated to God

# **Table of Contents**

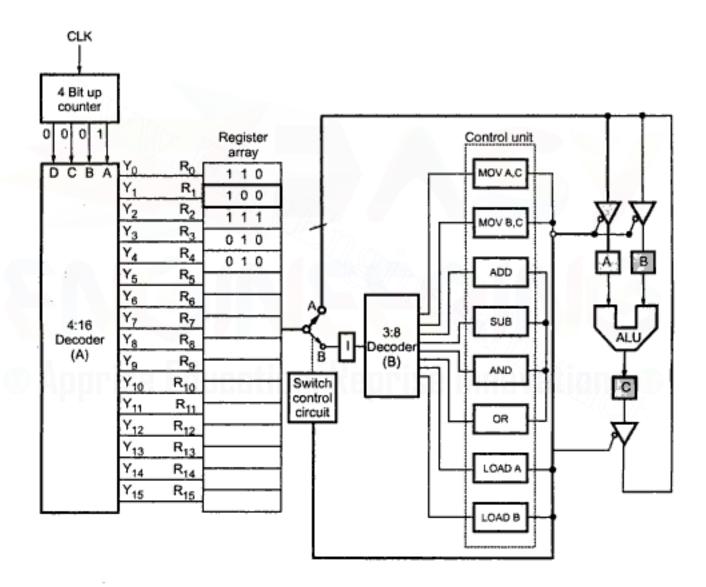

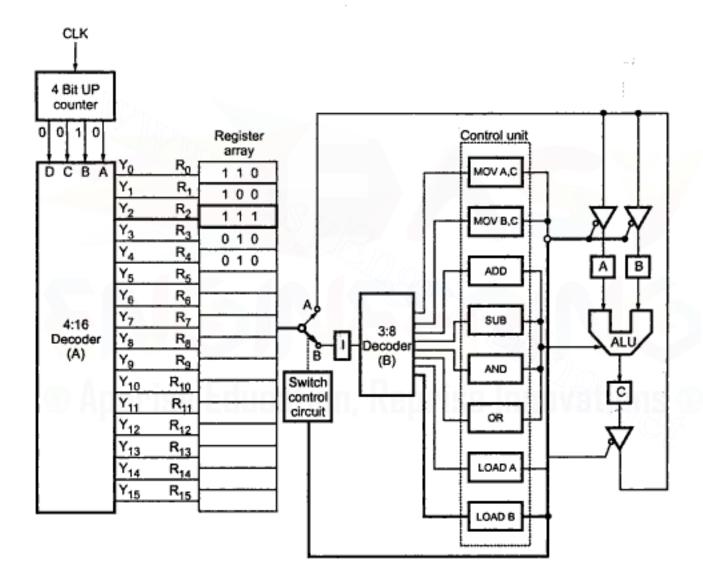

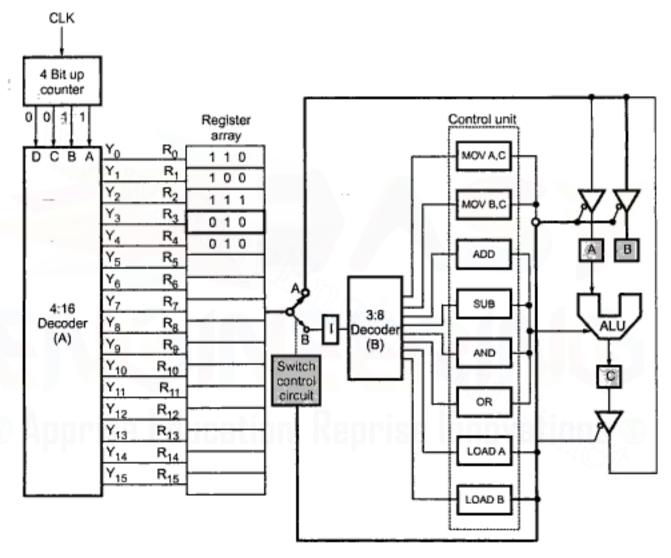

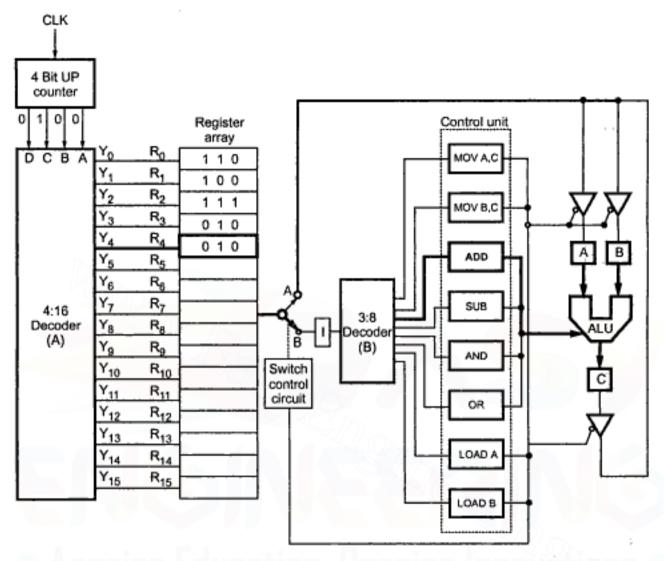

| chapter-r introduction to microprocessor & microcomputer sys | steins (1 - 1) to (1 - 20) |

|--------------------------------------------------------------|----------------------------|

| 1.1 Introduction to Microprocessor                           |                            |

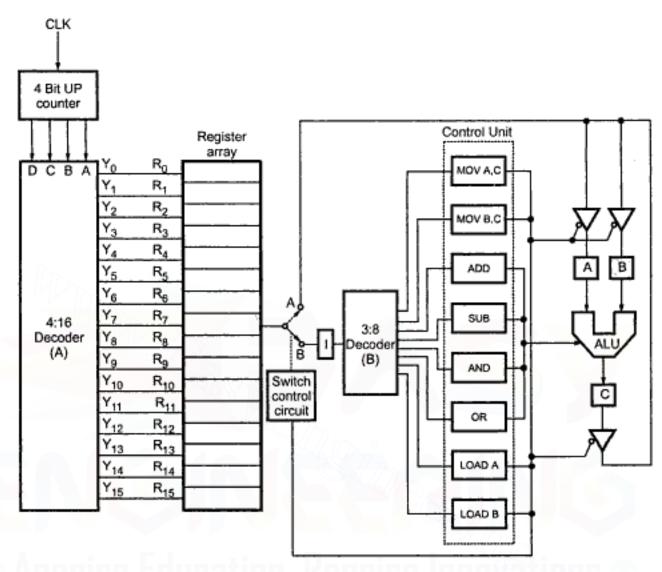

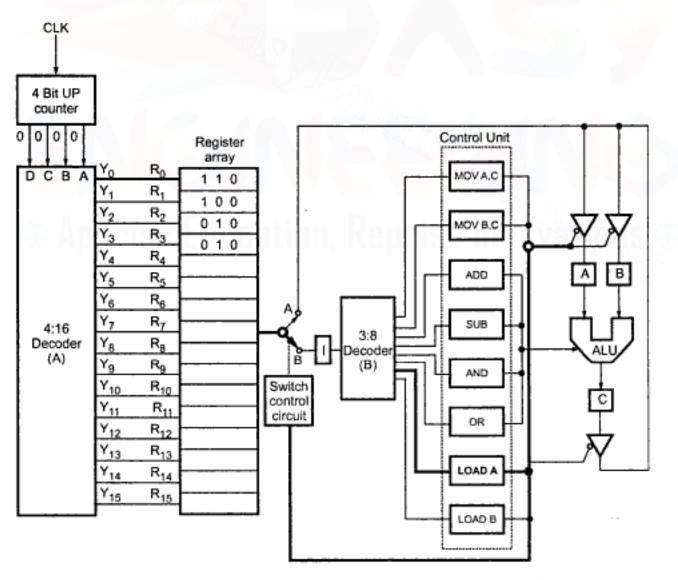

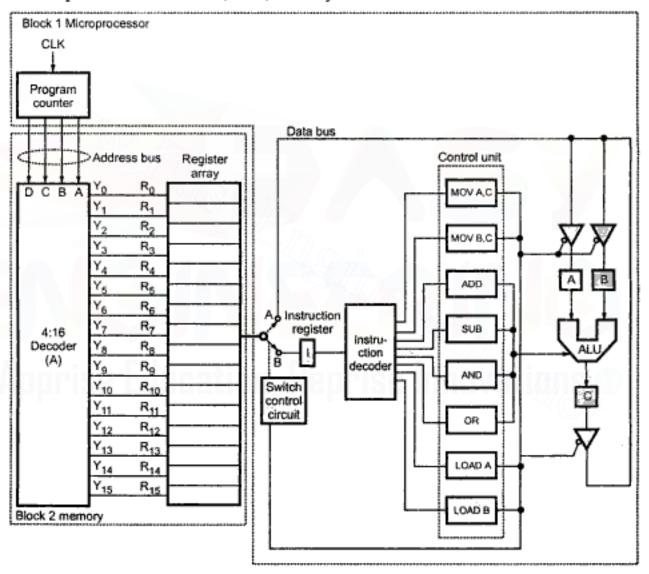

| 1.1.1 Simple Model of Microprocessor                         |                            |

| 1.1.1.1 Counter                                              |                            |

| 1.1.1.2 Decoder A.                                           | 1-4                        |

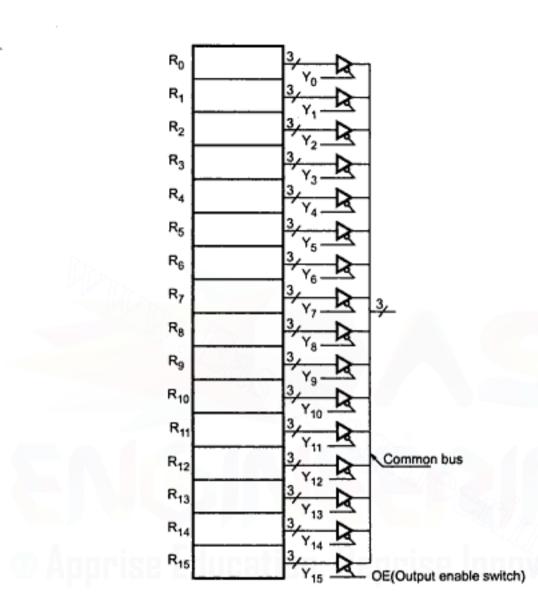

| 1.1.1.3 Register Array                                       | 1-4                        |

| 1.1.1.4 Common Bus                                           |                            |

| 1.1.1.5 Register I                                           |                            |

| 1.1.1.6 Decoder B                                            |                            |

| 1.1.1.7 Control Unit                                         |                            |

| 1.1.1.8 Switch Control Circuit                               |                            |

| 1.1.1.9 ALU                                                  |                            |

|                                                              |                            |

| 1.1.1.10 Operation                                           |                            |

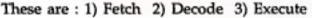

| 1.1.3 Different Phases in the Execution Process              |                            |

| 1.1.3.1 Fetch                                                |                            |

| 1.1.3.2 Decode                                               |                            |

| 1.1.3.3 Execute                                              |                            |

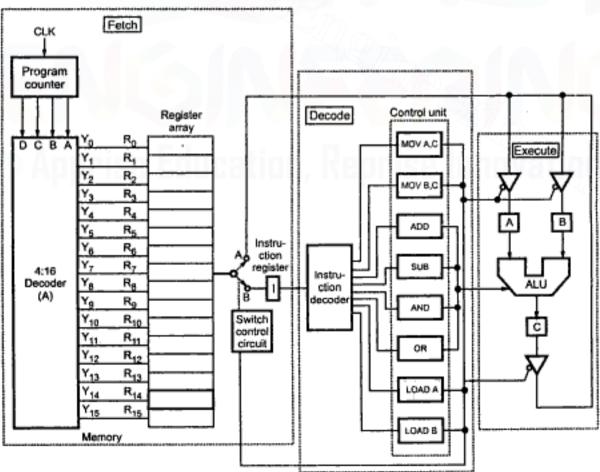

| 1.1.4 Microprocessor Architecture and its Operation          |                            |

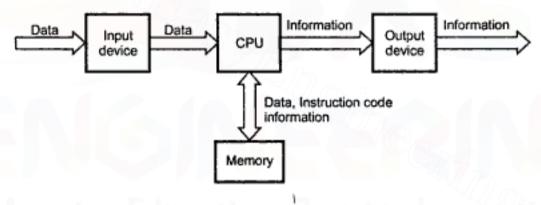

| 1.2 Microcomputer Systems                                    |                            |

| Review Questions                                             |                            |

| Chapter-2 8085 Microprocessor                                |                            |

| Gilapter-2 aves microprocessor                               | [Z = 1] to [Z = 30]        |

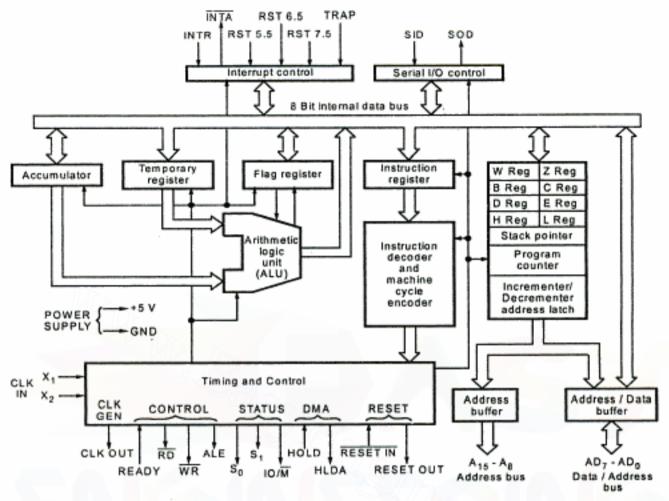

| 2.1 Introduction                                             |                            |

| 2.2 Features of 8085                                         |                            |

| 2.3 Architecture of 8085                                     |                            |

| 2.3.1 Register Structure.                                    |                            |

| 2.3.2 Arithmetic Logic Unit (ALU)                            |                            |

| 2.3.3 Instruction Decoder                                    |                            |

| 2.3.4 Address Buffer                                         |                            |

|                                                              | ····· ···· ····· ···· ···· |

| 2.3.5 Address/Data Buffer                                                                   |

|---------------------------------------------------------------------------------------------|

| 2.3.6 Incrementer/Decrementer Address Latch. 2 - 3                                          |

| 2.3.7 Interrupt Control                                                                     |

| 2.3.8 Serial I/O Control                                                                    |

| 2.3.9 Timing and Control Circuitry                                                          |

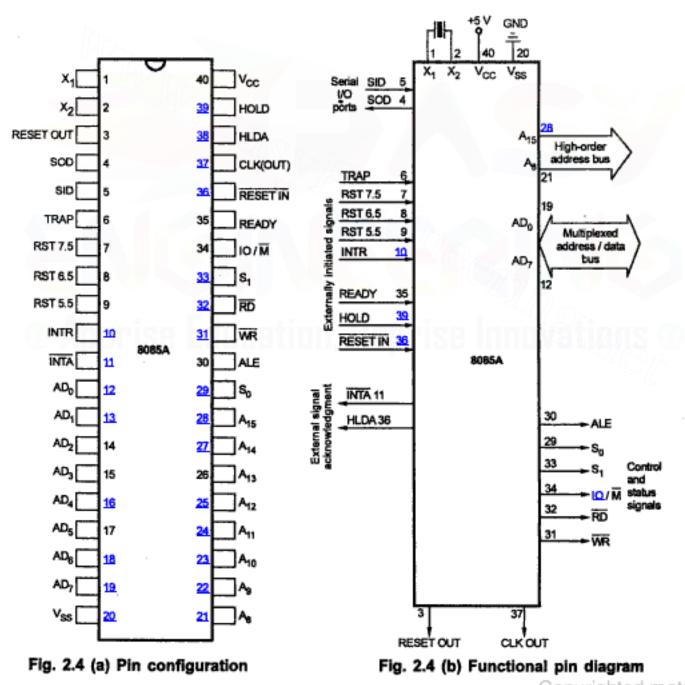

| 2.4 Pin Definitions of 8085                                                                 |

| 2.4.1 Power Supply and Frequency Signals 2 - 9                                              |

| 2.4.2 Data Bus and Address Bus 2 - 9                                                        |

| 2.4.3 Control and Status Signals 2 - 9                                                      |

| 2.4.4 Interrupt Signals 2 - 10                                                              |

| 2.4.5 Serial I/O Signals                                                                    |

| 2.4.6 DMA Signal                                                                            |

| 2.4.7 Reset Signals                                                                         |

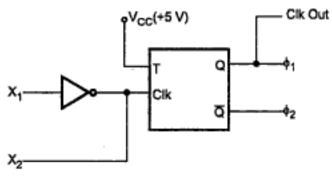

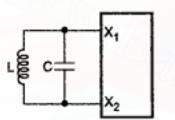

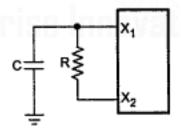

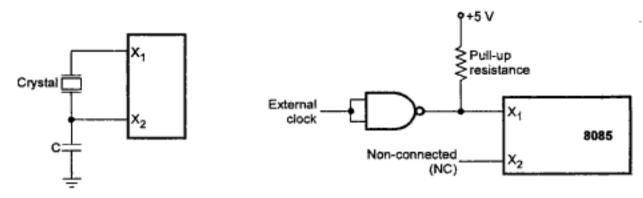

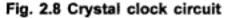

| 2.5 Clock Circuits                                                                          |

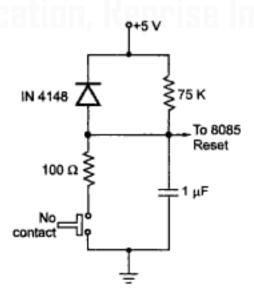

| 2.6 Reset Circuit                                                                           |

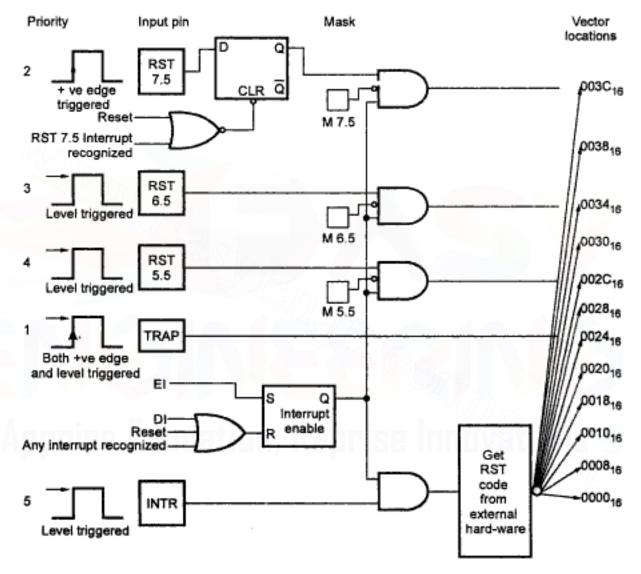

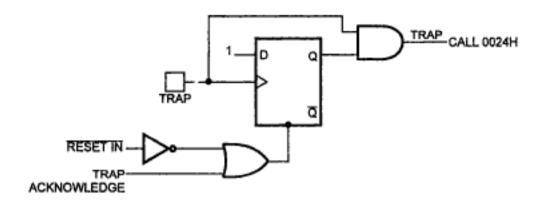

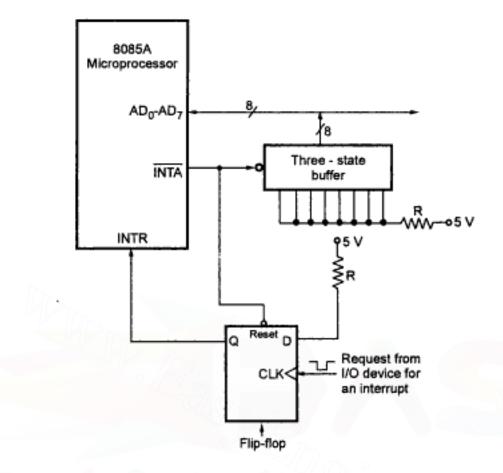

| 2.7 8085 Interrupt Structure and Operation                                                  |

| 2.7.1 Types of Interrupts                                                                   |

| 2.7.2 Overall Interrupt Structure                                                           |

| 2.7.2.1 Hardware Interrupts in 8085                                                         |

| 2.7.2.2 Software Interrupts in 8085                                                         |

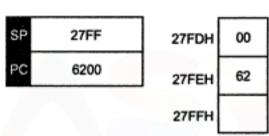

| 2.7.3 Masking / Unmasking of Interrupts                                                     |

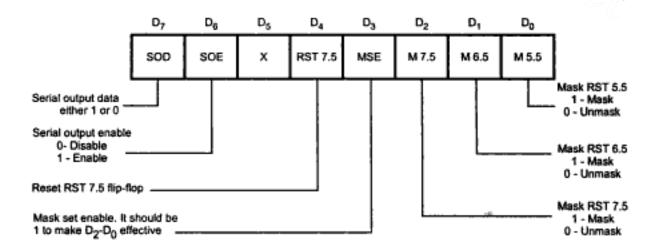

| 2.7.4 Pending Interrupts 2 - 1                                                              |

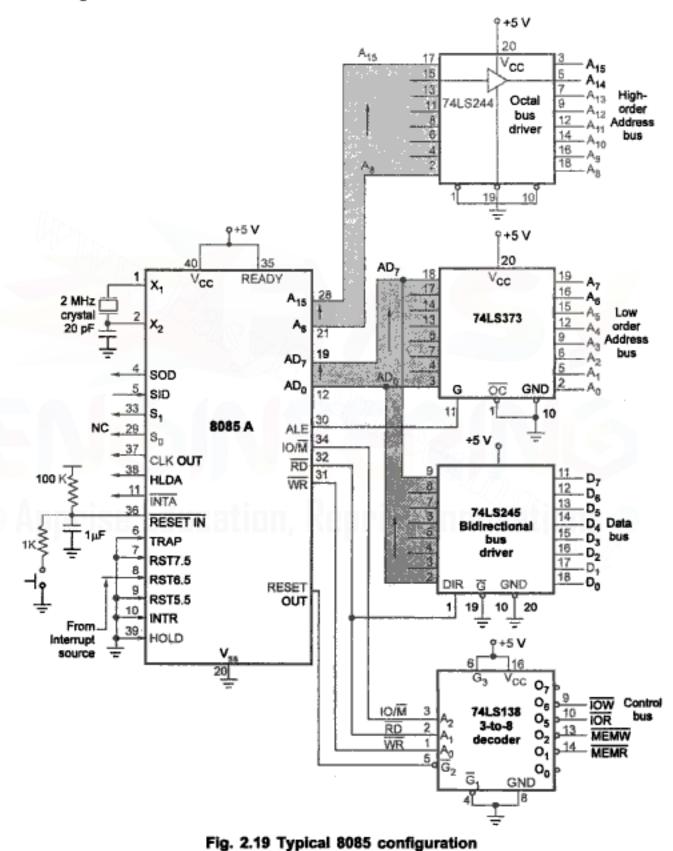

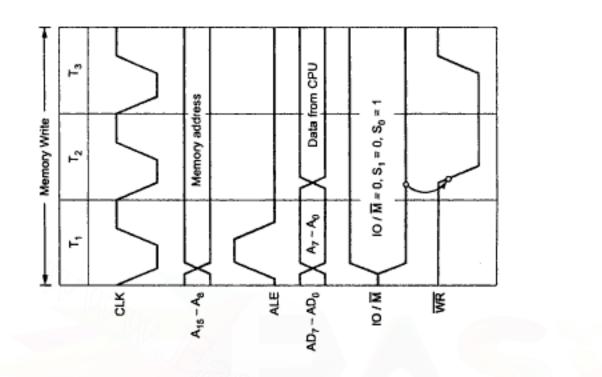

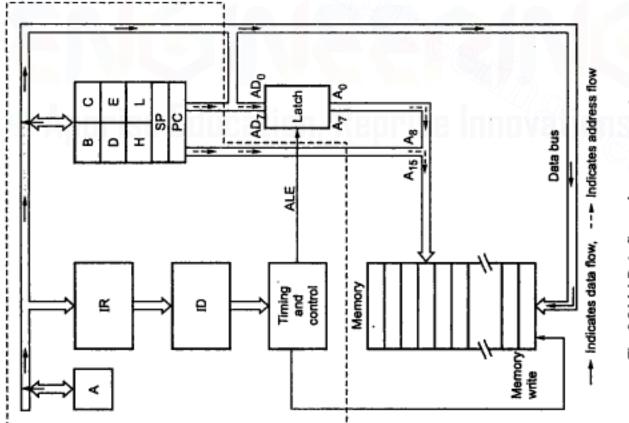

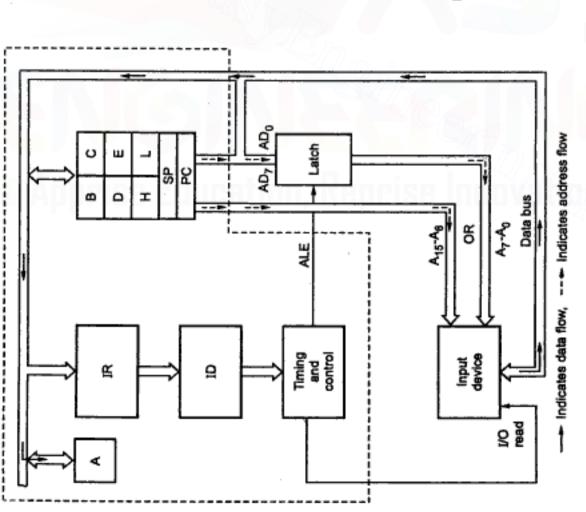

| 2.8 I/O, Memory and System Buses 2 - 19                                                     |

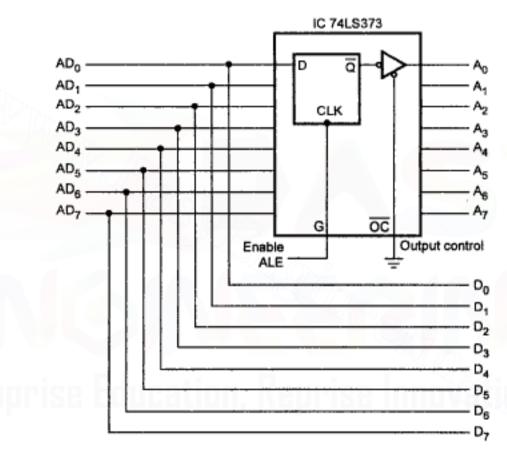

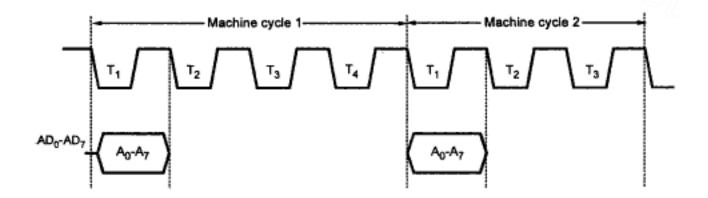

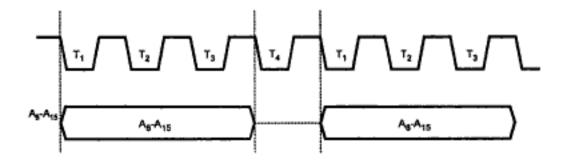

| 2.8.1 Generation of Address and Data Bus - Demultiplexing AD <sub>7</sub> - AD <sub>0</sub> |

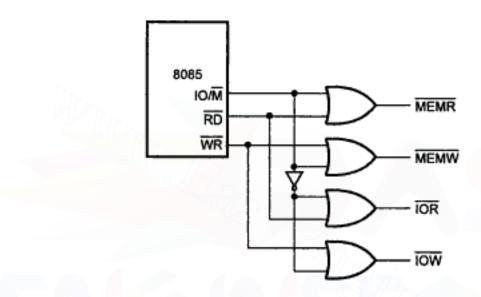

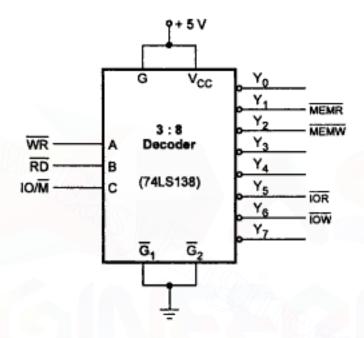

| 2.8.2 Generation of Control Signals 2 - 2                                                   |

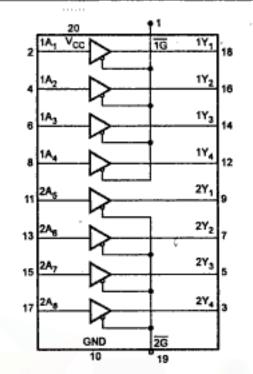

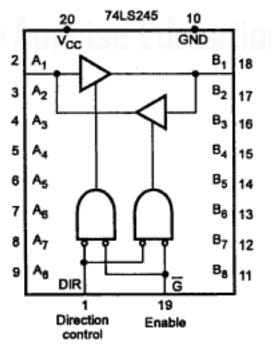

| 2.8.3 Bus Drivers                                                                           |

| 2.8.4 Typical Configuration 2 - 2                                                           |

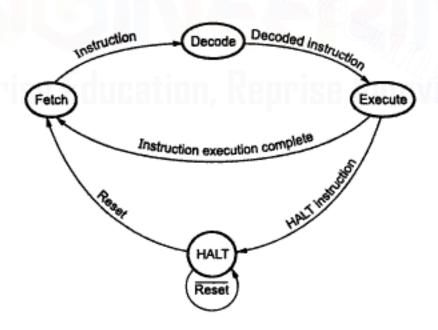

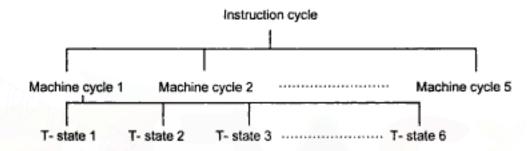

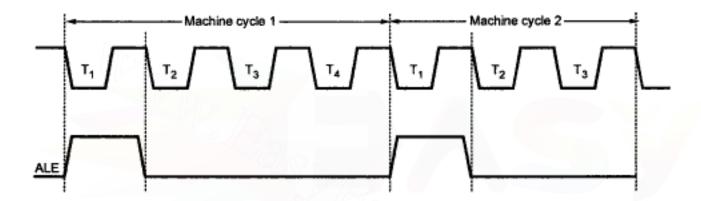

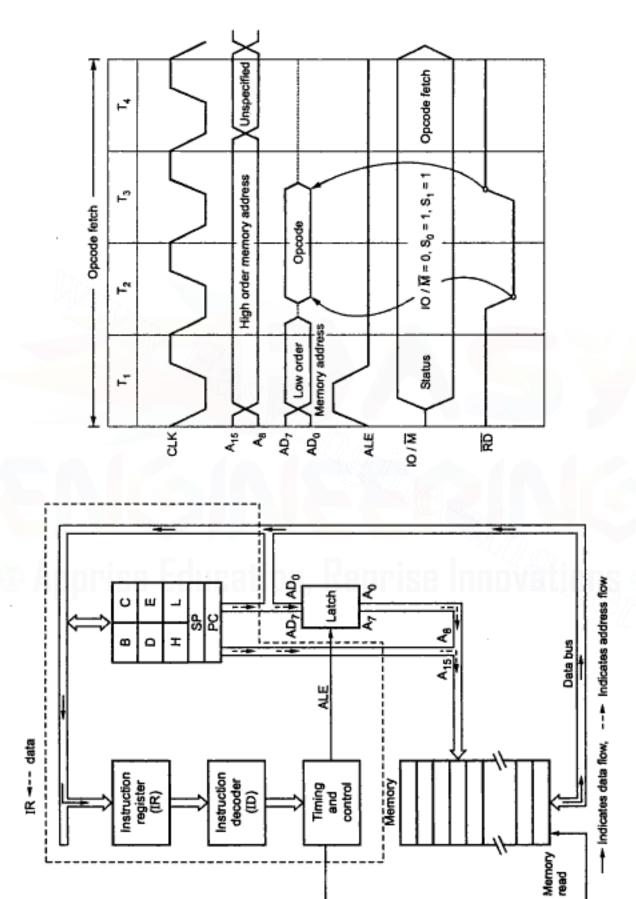

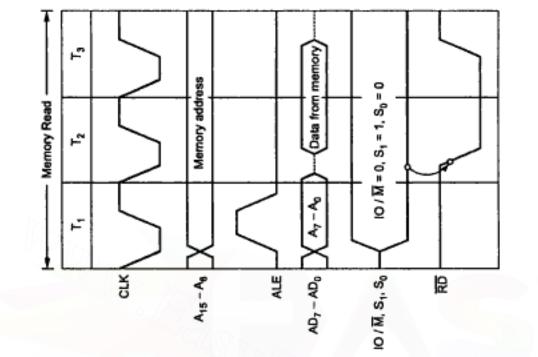

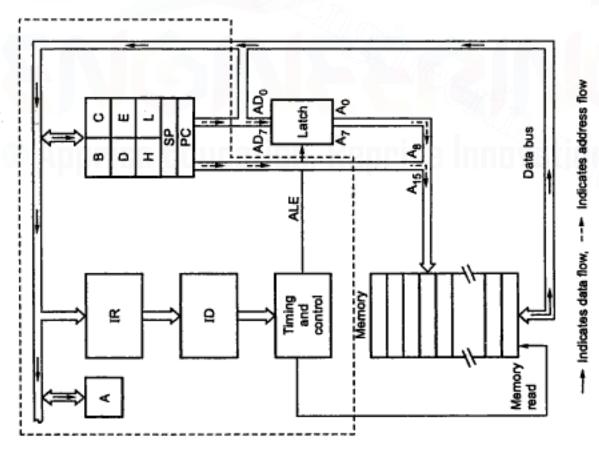

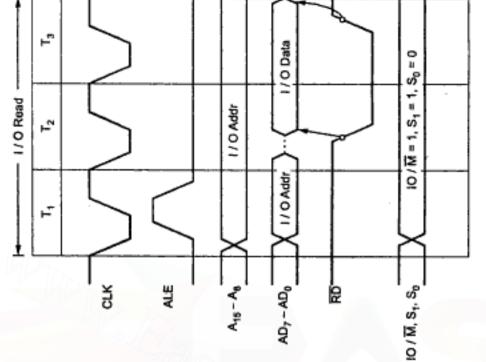

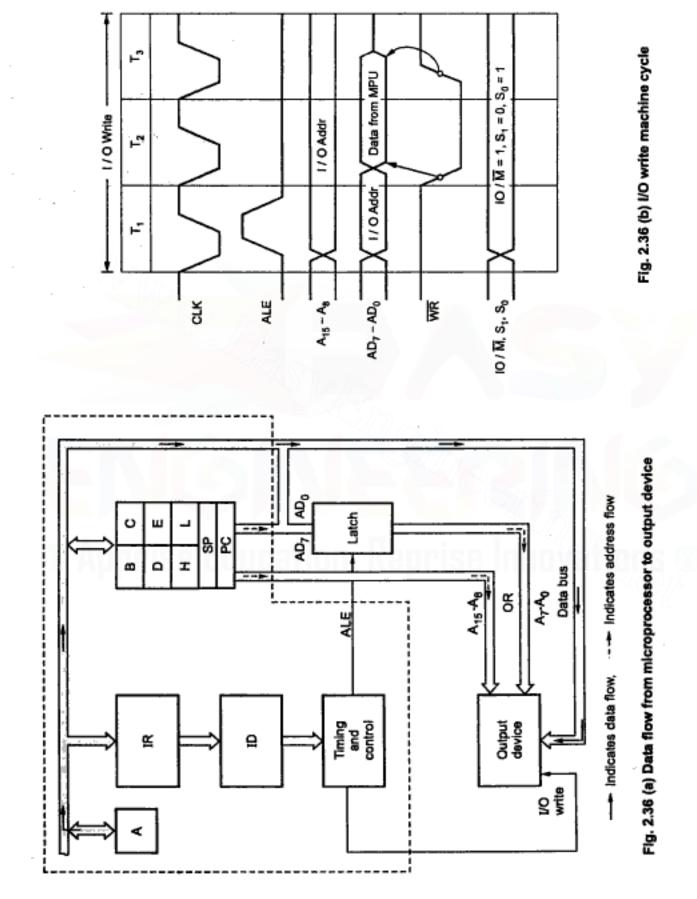

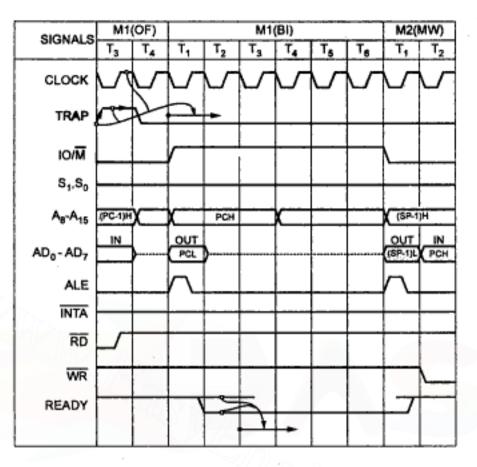

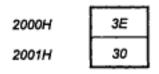

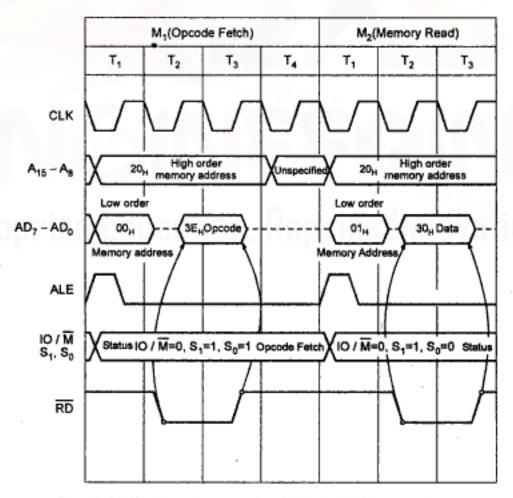

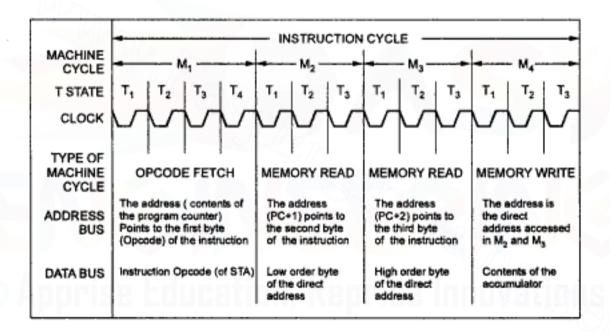

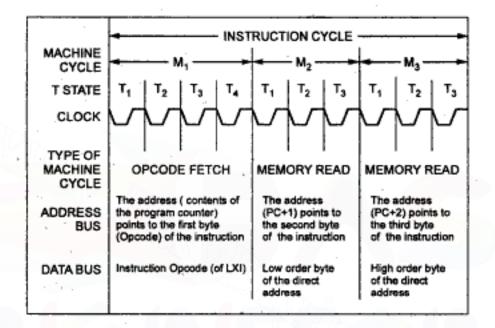

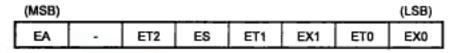

| 2.9 Instruction Cycle                                                                       |

| 2.10 Instruction, Execution, Sequence and Data Flow                                         |

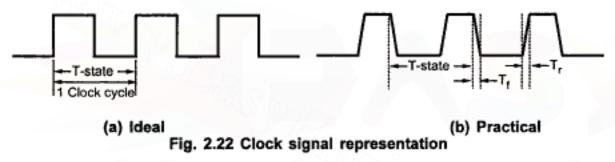

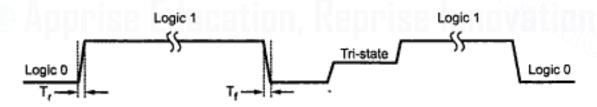

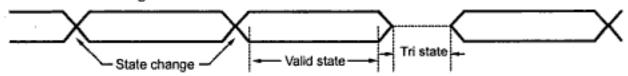

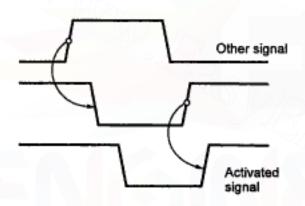

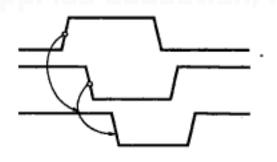

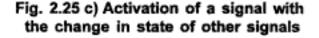

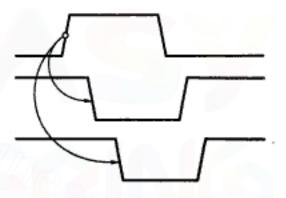

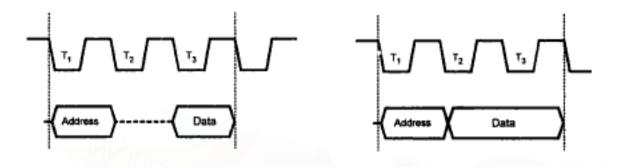

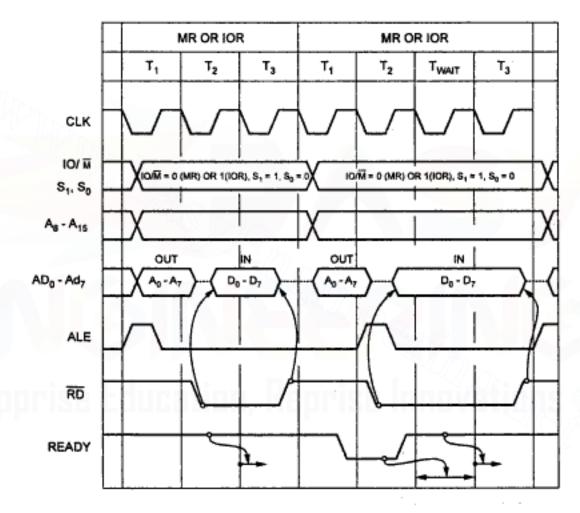

| 2.10.1 Representation of Signals 2 - 2                                                      |

| 2.10.2 Signa: Timings                                                                       |

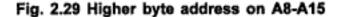

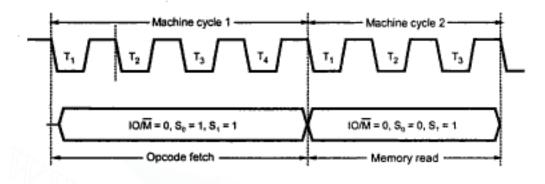

| 2.10.3 Machine Cycles                                                                       |

| 2.10.4 Concept of Wait States                                                               |

| Review Questions 2 - 49                                                                     |

ų

| pter-3 8085 Instruction Set and ALP (3 - 1) to (3 - 68      |

|-------------------------------------------------------------|

| 3.1 Introduction                                            |

| 3.2 Instruction Classification                              |

| 3.2.1 Data Transfer Operations                              |

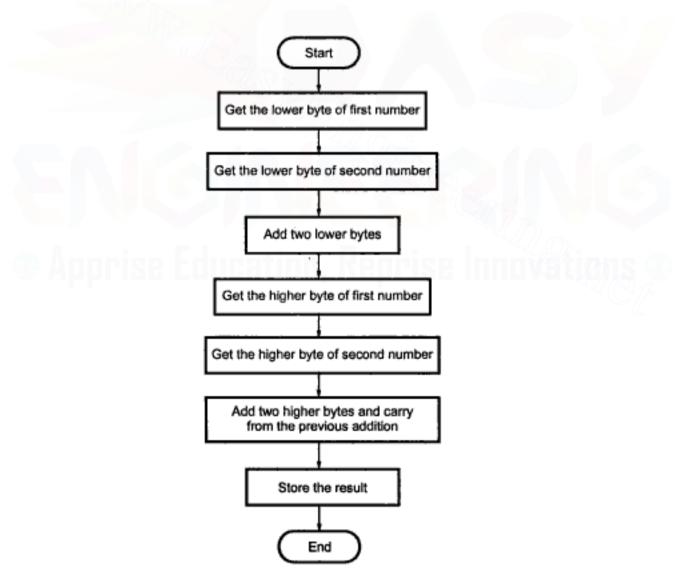

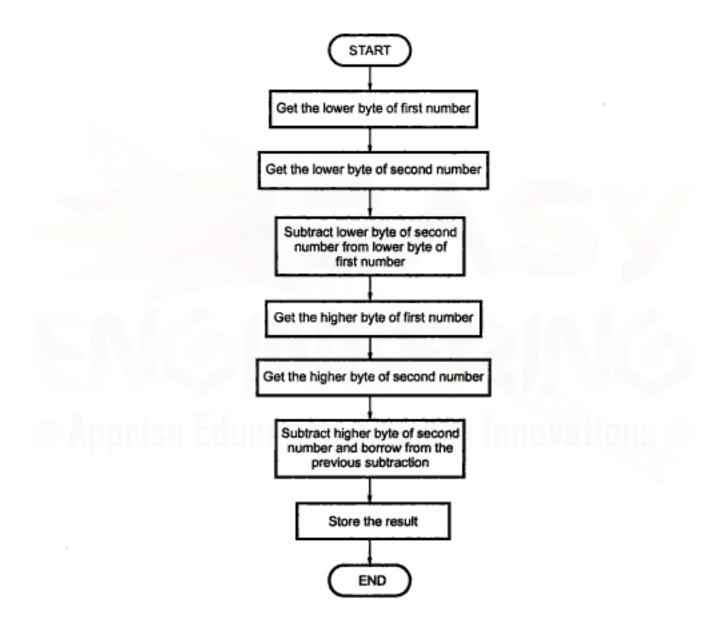

| 3.2.2 Arithmetic Operations                                 |

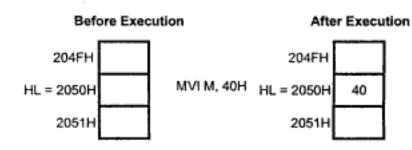

| 3.2.3 Logical Operations                                    |

| 3.2.4 Branching Operations                                  |

| 3.2.5 Stack, Input/Output and Machine Control Operations    |

| 3.3 Instruction and Data Format                             |

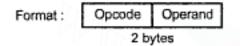

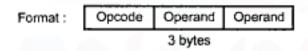

| 3.3.1 Instruction Formats                                   |

| 3.3.2 Opcode Formats                                        |

| 3.3.3 Data Formats                                          |

| 3.4 Instruction Set of 80853 - 8                            |

| 3.4.1 Data Transfer Group                                   |

| 3.4.2 Arithmetic Group                                      |

| 3.4.3 Logic Group                                           |

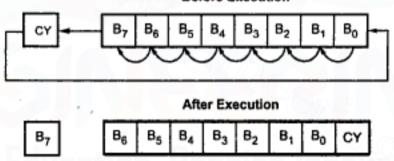

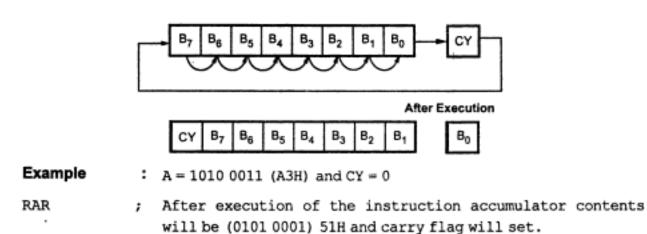

| 3.4.4 Rotate Group                                          |

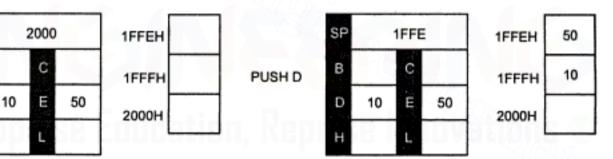

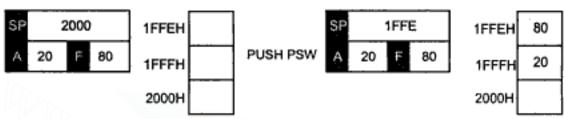

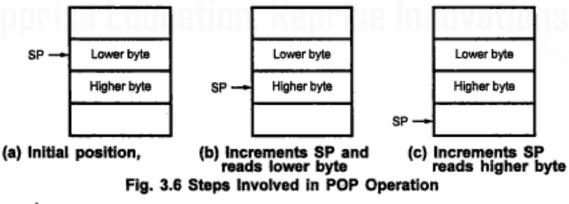

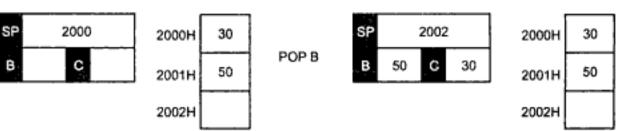

| 3.4.5 Stack Operations                                      |

| 3.4.6 Branch Group                                          |

| 3.4.7 Input/Output                                          |

| 3.4.8 Machine Control Group                                 |

| 3.5 Addressing Modes                                        |

| 3 - 37                                                      |

| 3.7 Assembly Language Programming                           |

| 3.7.1 Steps Involved in Programming                         |

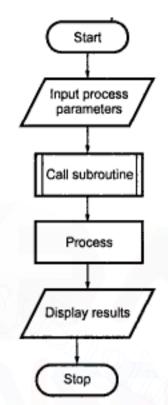

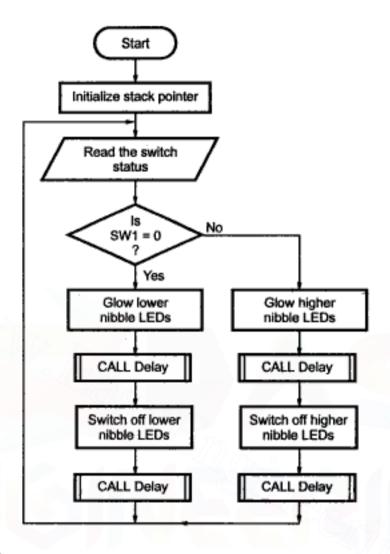

| 3.7.2 Flowchart                                             |

| 3.7.3 Assembly Language Program                             |

| 3.7.4 Assembly Language Program to Machine Language Program |

| 3.7.5 Storing Hex Code in the Memory                        |

| 3.7.6 Executing the Program                                 |

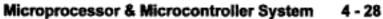

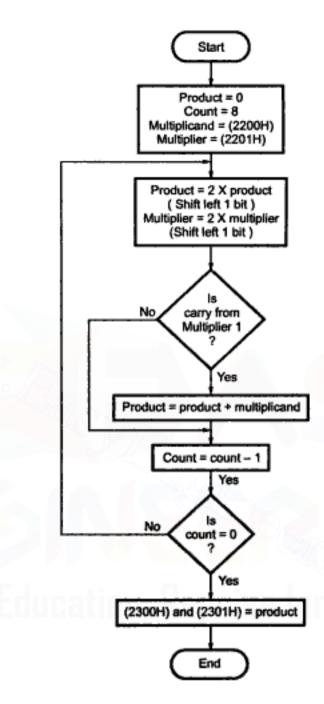

| 3.8 Programming Examples 3 - 46                             |

| 3.9 Instruction Comparisons                                 |

| Review Questions                                            |

····· (vi)

| Chapter-4 Programming Techniques (4 - 1) to (4 - 56)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

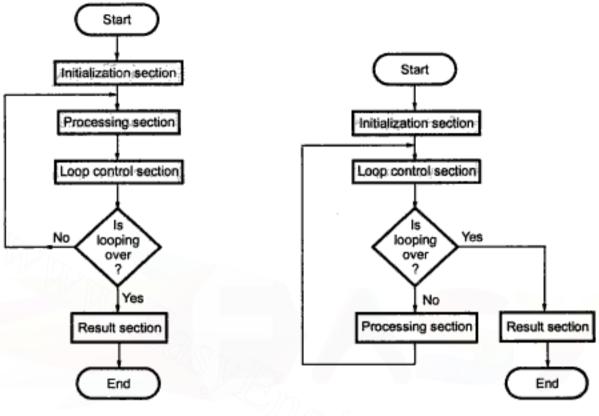

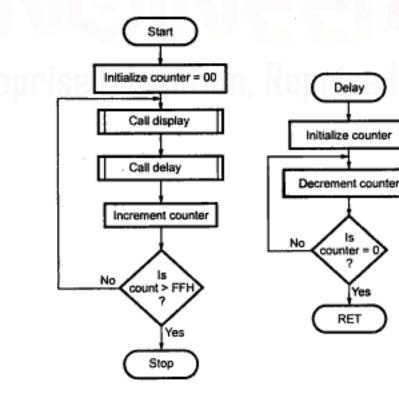

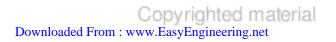

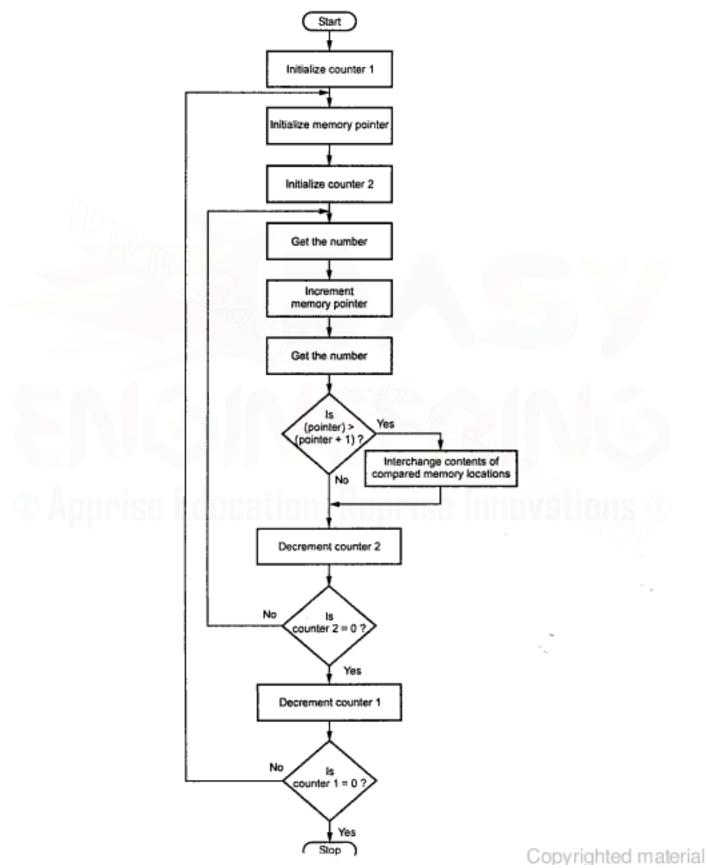

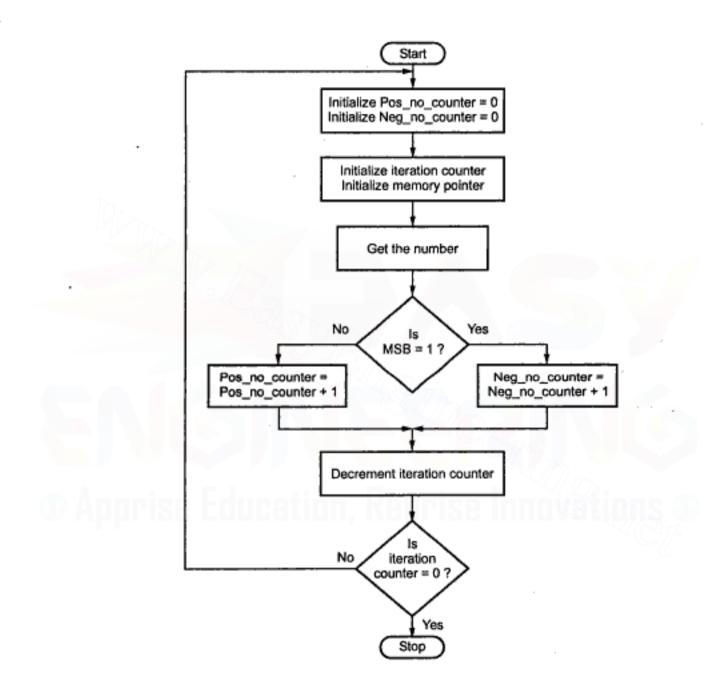

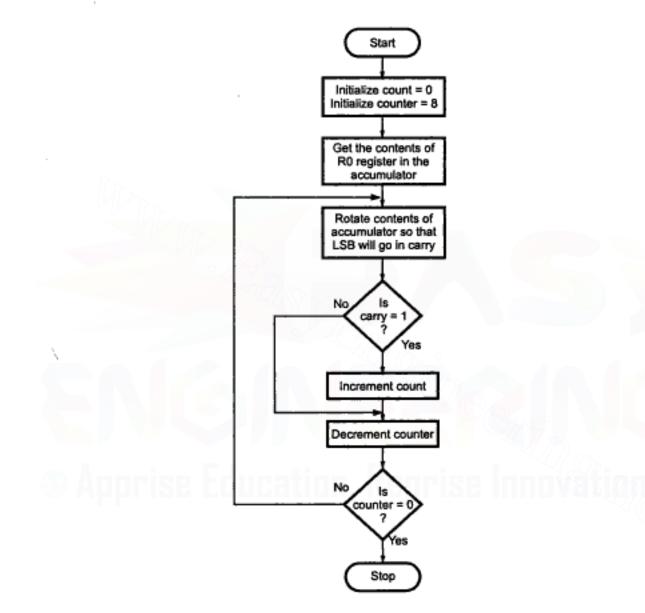

| 4.1 Looping, Counting and Indexing 4 - 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 4.2 Timers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 4.2.1 Timer Delay using NOP Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 4.2.2 Timer Delay using Counters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 4.2.3 Timer Delay using Nested Loops                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

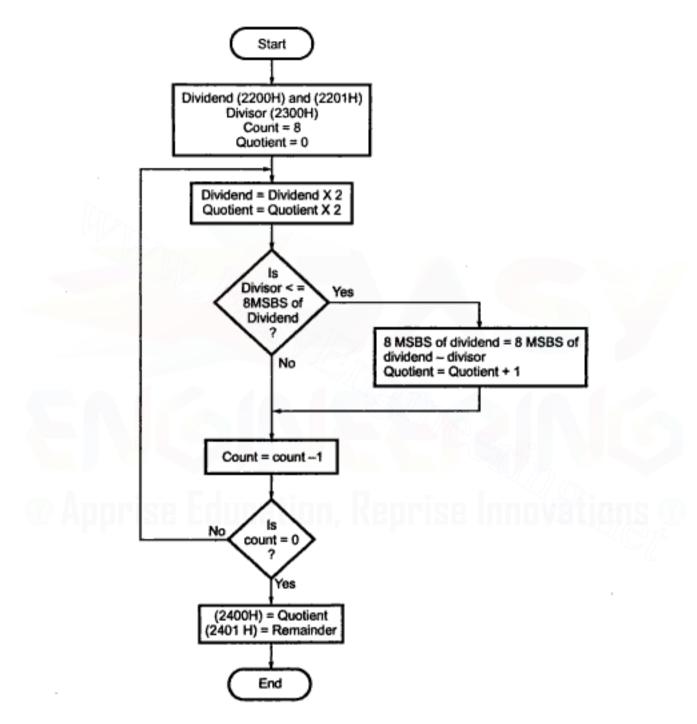

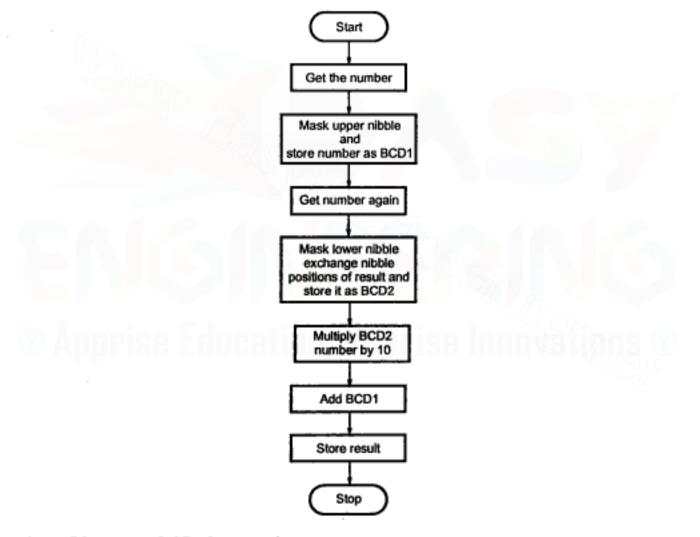

| 4.3 Code Conversion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 4.3.1 BCD to Binary Conversion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

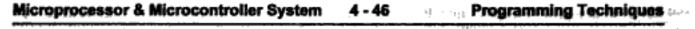

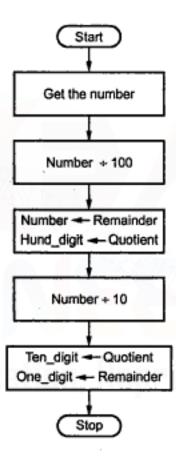

| 4.3.2 Binary to BCD Conversion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

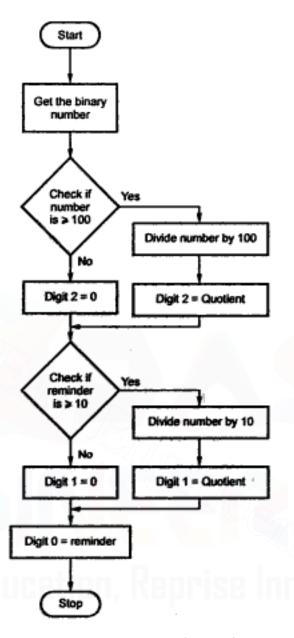

| 4.3.3 BCD to Seven Segment Conversion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

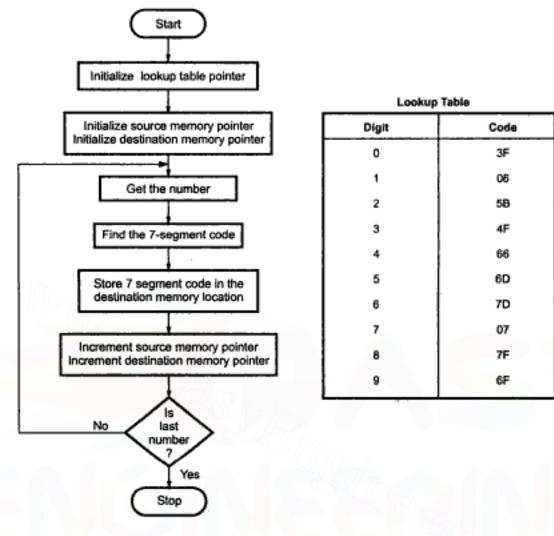

| 4.3.4 Binary to ASCII Code Conversion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 4.3.5 ASCII Code to Binary Conversion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

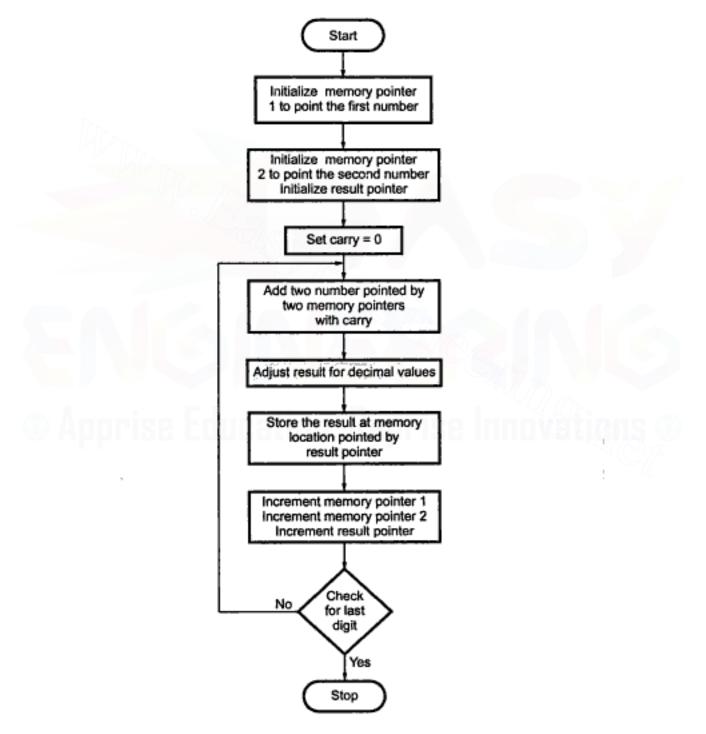

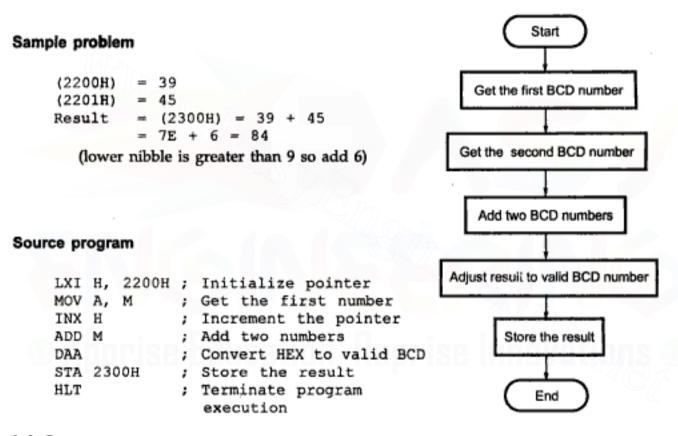

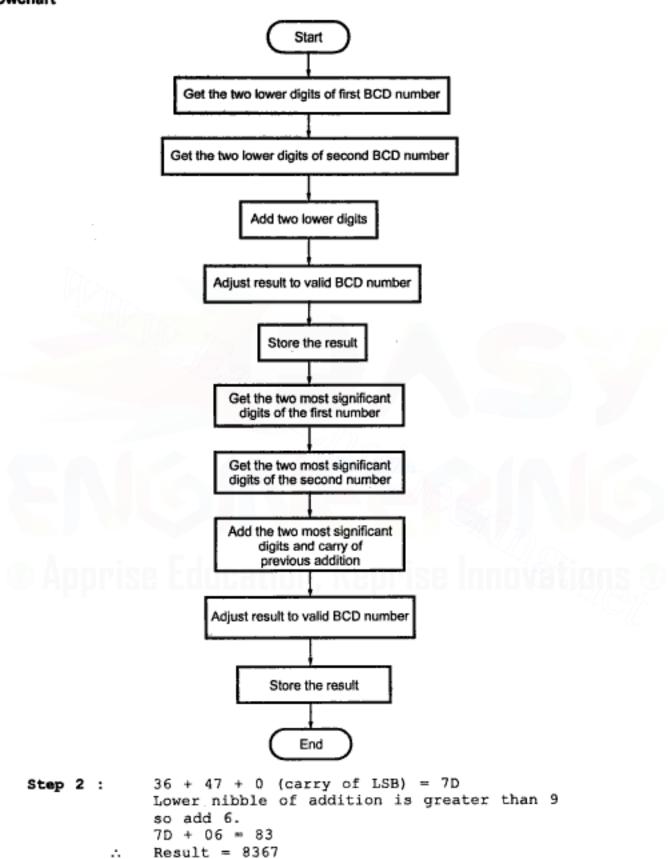

| 4.4 BCD Arithmetic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 4.4.1 BCD Addition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 4.4.2 BCD Subtraction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Review Questions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Neview Questions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Chapter-5 Stacks and Subroutines (5 - 1) to (5 - 22)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Chapter-5       Stacks and Subroutines       (5 - 1) to (5 - 22)         5.1 Concept of Stack and Subroutines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Chapter-5       Stacks and Subroutines       (5 - 1) to (5 - 22)         5.1       Concept of Stack and Subroutines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Chapter-5       Stacks and Subroutines       (5 - 1) to (5 - 22)         5.1       Concept of Stack and Subroutines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

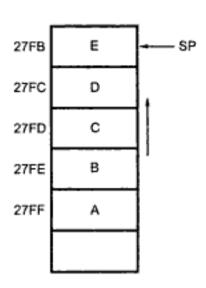

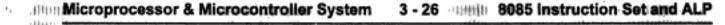

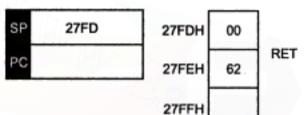

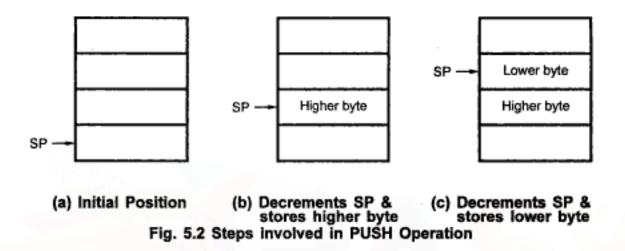

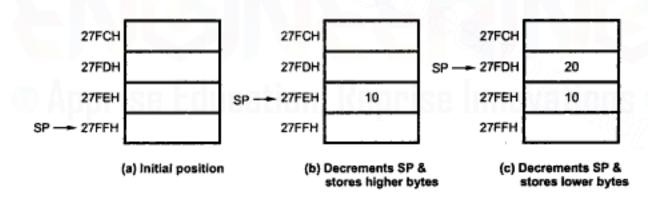

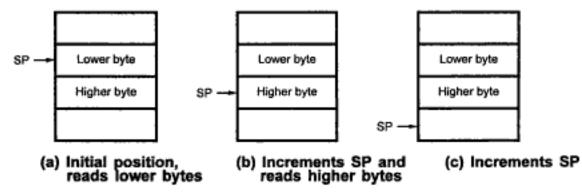

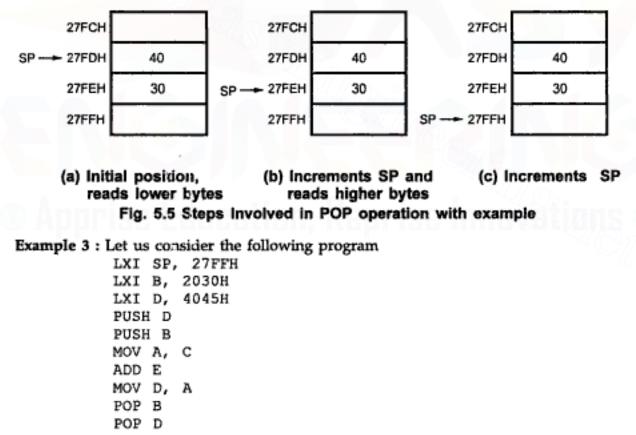

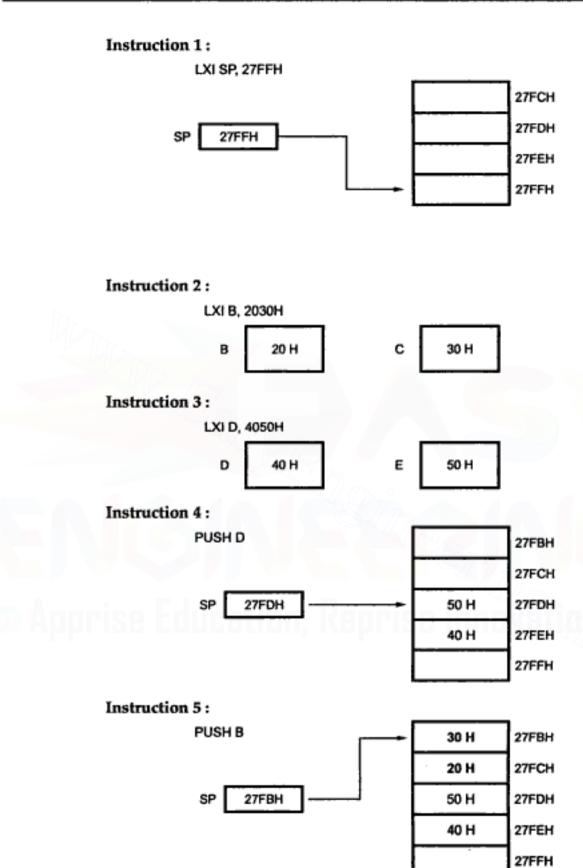

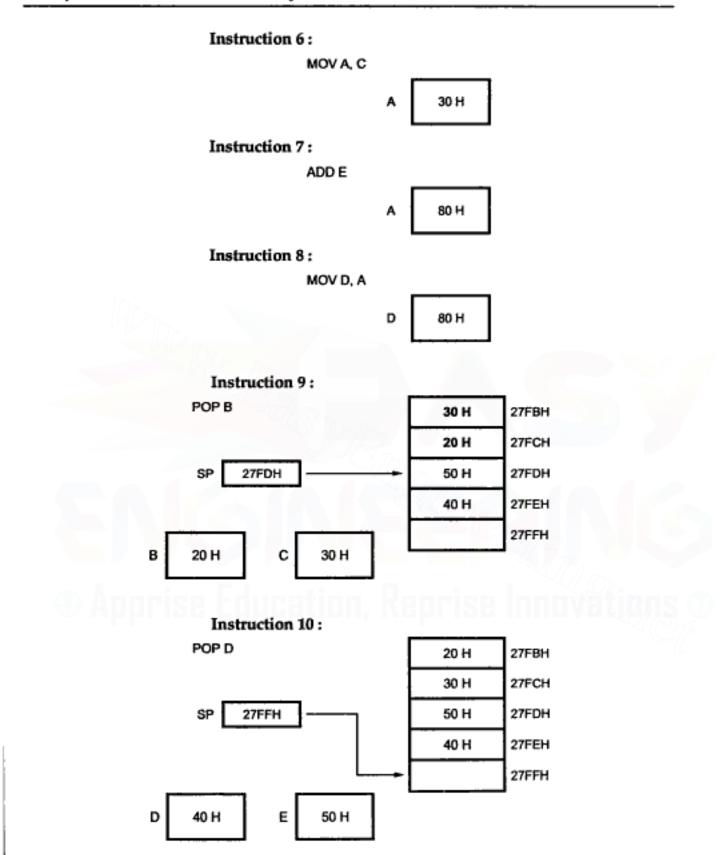

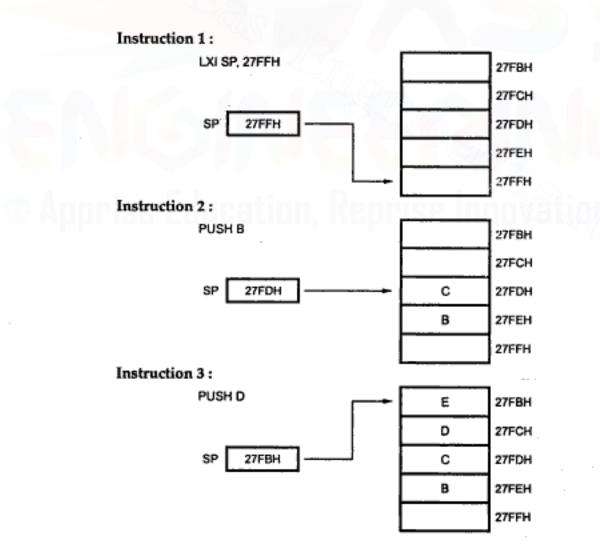

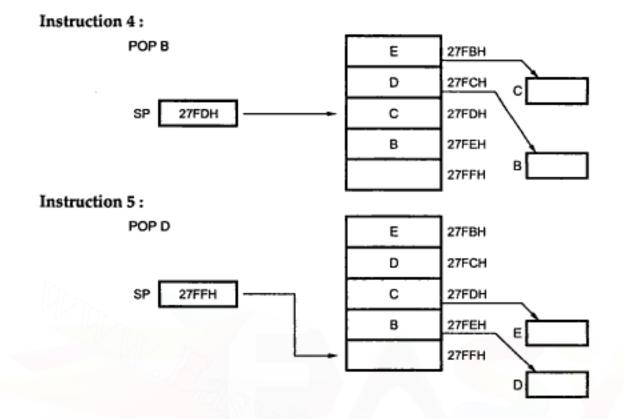

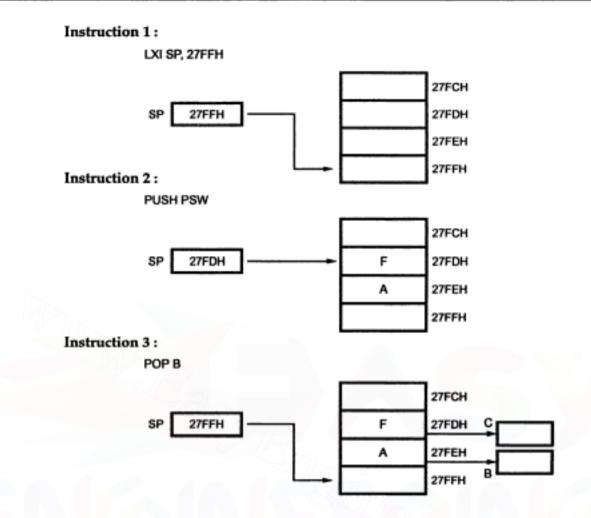

| Chapter-5       Stacks and Subroutines       (5 - 1) to (5 - 22)         5.1 Concept of Stack and Subroutines       .5 - 1         5.1.1 Stack       .5 - 1         5.1.1 Stack       .5 - 1         5.1.1 Stack Related Instructions       .5 - 2         5.1.1.2 Detail Operation and the use of Stack Related Instructions       .5 - 3                                                                                                                                                                                                                                                                                                                                                                                      |

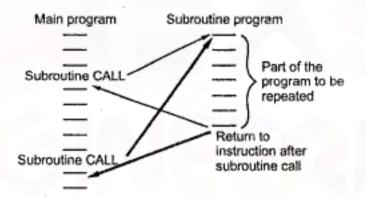

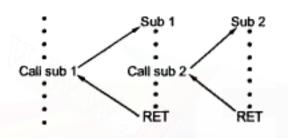

| Chapter-5       Stacks and Subroutines       (5 - 1) to (5 - 22)         5.1       Concept of Stack and Subroutines       .5 - 1         5.1.1       Stack       .5 - 1         5.1.1       Stack Related Instructions       .5 - 2         5.1.1       Stack Related Instructions       .5 - 3         5.1.2       Subroutines       .5 - 11                                                                                                                                                                                                                                                                                                                                                                                   |

| Chapter-5       Stacks and Subroutines       (5 - 1) to (5 - 22)         5.1 Concept of Stack and Subroutines       .5 - 1         5.1.1 Stack       .5 - 1         5.1.1 Stack Related Instructions       .5 - 2         5.1.1 Stack Related Instructions       .5 - 3         5.1.2 Detail Operation and the use of Stack Related Instructions       .5 - 11         5.2 Parameters Passing Techniques       .5 - 13                                                                                                                                                                                                                                                                                                          |

| Image: Stacks and Subroutines       (5 - 1) to (5 - 22)         5.1 Concept of Stack and Subroutines       .5 - 1         5.1.1 Stack       .5 - 1         5.1.1 Stack Related Instructions       .5 - 2         5.1.1 Stack Related Instructions       .5 - 3         5.1.2 Detail Operation and the use of Stack Related Instructions       .5 - 11         5.2 Parameters Passing Techniques       .5 - 13         5.2.1 Passing Parameters using Registers       .5 - 13                                                                                                                                                                                                                                                    |

| Chapter-5       Stacks and Subroutines       (5 - 1) to (5 - 22)         5.1 Concept of Stack and Subroutines       .5 - 1         5.1.1 Stack       .5 - 1         5.1.1 Stack Related Instructions       .5 - 2         5.1.1 Stack Related Instructions       .5 - 3         5.1.2 Detail Operation and the use of Stack Related Instructions       .5 - 11         5.2 Parameters Passing Techniques       .5 - 13                                                                                                                                                                                                                                                                                                          |

| Impler-5       Stacks and Subroutines       (5 - 1) to (5 - 22)         5.1       Concept of Stack and Subroutines       5 - 1         5.1.1       Stack       5 - 1         5.1.1       Stack Related Instructions       5 - 2         5.1.1.2       Detail Operation and the use of Stack Related Instructions       5 - 3         5.1.2       Subroutines       5 - 11         5.2       Parameters Passing Techniques       5 - 13         5.2.2       Passing Parameters using Registers       5 - 13         5.2.2       Passing Parameters using Memory       5 - 14         5.2.3       Passing Parameters using Pointers       5 - 14                                                                                  |

| Stacks and Subroutines(5 - 1) to (5 - 22)5.1 Concept of Stack and Subroutines5 - 15.1.1 Stack5 - 15.1.1 Stack Related Instructions5 - 25.1.1 Detail Operation and the use of Stack Related Instructions5 - 35.1.2 Subroutines5 - 115.2 Parameters Passing Techniques5 - 135.2.1 Passing Parameters using Registers5 - 135.2.2 Passing Parameters using Memory5 - 145.2.4 Passing Parameters using Stack5 - 15                                                                                                                                                                                                                                                                                                                   |

| Stacks and Subroutines(5 - 1) to (5 - 22)5.1 Concept of Stack and Subroutines5 - 15.1.1 Stack5 - 15.1.1 Stack Related Instructions5 - 25.1.1.2 Detail Operation and the use of Stack Related Instructions5 - 35.1.2 Subroutines5 - 115.2 Parameters Passing Techniques5 - 135.2.1 Passing Parameters using Registers5 - 135.2.2 Passing Parameters using Memory5 - 145.2.3 Passing Parameters using Stack5 - 155.3 Subroutine Documentation5 - 17                                                                                                                                                                                                                                                                               |

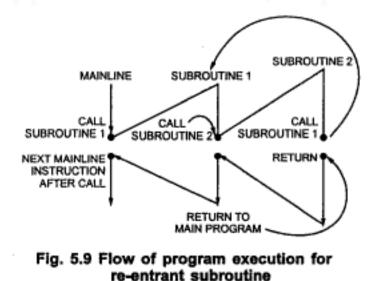

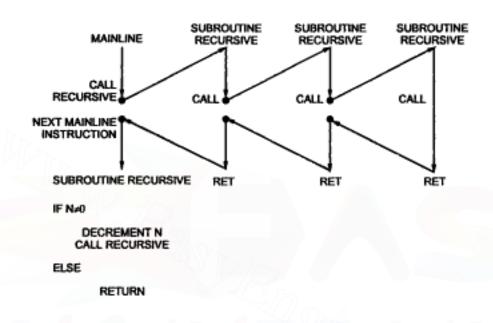

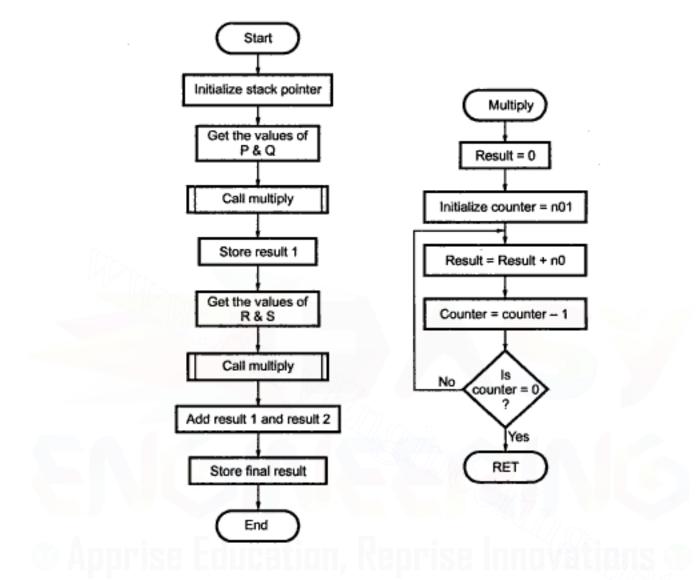

| Chapter-5       Stacks and Subroutines       (5 - 1) to (5 - 22)         5.1       Concept of Stack and Subroutines       5 - 1         5.1.1       Stack       5 - 1         5.1.1       Stack Related Instructions       5 - 2         5.1.1       Stack Related Instructions       5 - 3         5.1.2       Subroutines       5 - 13         5.2       Parameters Passing Techniques       5 - 13         5.2.1       Passing Parameters using Registers       5 - 13         5.2.2       Passing Parameters using Mernory       5 - 14         5.2.3       Passing Parameters using Stack       5 - 15         5.3       Subroutine Documentation       5 - 17         5.4       Advanced Subroutine Concepts       5 - 18 |

| Stacks and Subroutines(5 - 1) to (5 - 22)5.1 Concept of Stack and Subroutines5 - 15.1.1 Stack5 - 15.1.1 Stack Related Instructions5 - 25.1.1.2 Detail Operation and the use of Stack Related Instructions5 - 35.1.2 Subroutines5 - 115.2 Parameters Passing Techniques5 - 135.2.1 Passing Parameters using Registers5 - 135.2.2 Passing Parameters using Memory5 - 145.2.3 Passing Parameters using Stack5 - 155.3 Subroutine Documentation5 - 17                                                                                                                                                                                                                                                                               |

(11)

| Chapter-6 I/O and Memory Interface (6 - 1) to (6 - 38)           |

|------------------------------------------------------------------|

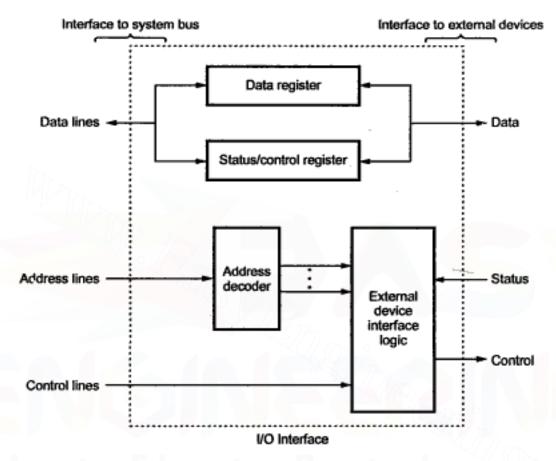

| 6.1 Introduction                                                 |

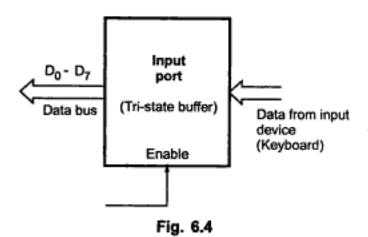

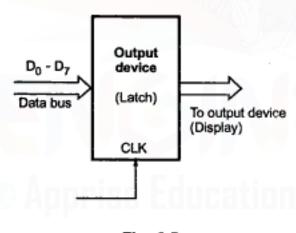

| 6.1.1 Input / Output System                                      |

| 6-2                                                              |

| 6.1.3 I/O Ports                                                  |

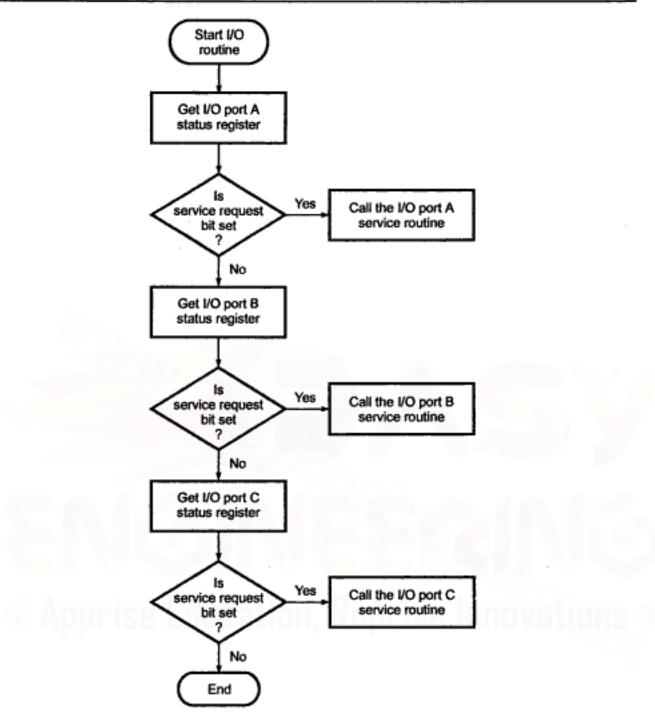

| 6.2 I/O Data Transfer Techniques                                 |

| 6.2.1 Programmed I/O                                             |

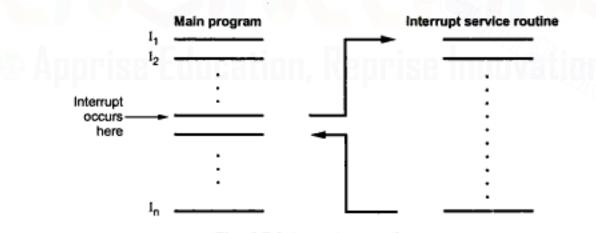

| 6.2.2 Interrupt Driven I/O                                       |

| 6.2.3 Comparison between Programmed I/O and Interrupt Driven I/O |

| 6.2.4 DMA Transfer                                               |

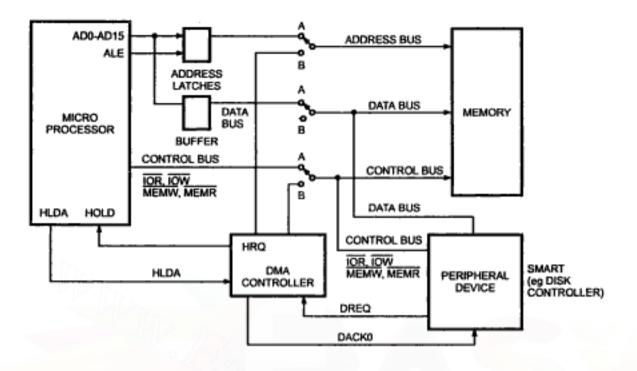

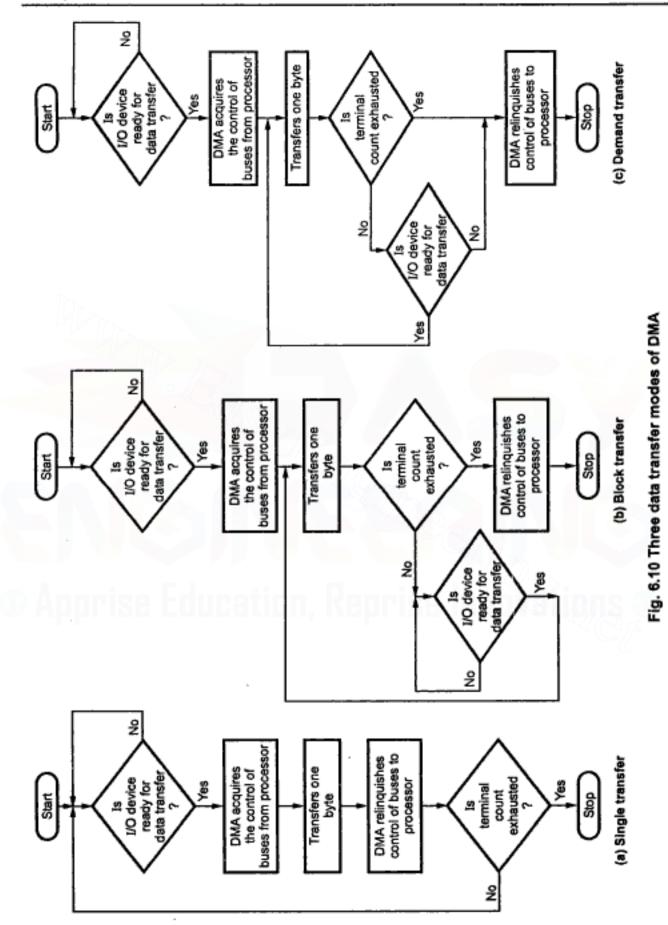

| 6.2.4.1 Hardware Controlled Data Transfer                        |

| 6.2.4.2 DMA idle Cycle                                           |

| 6.2.4.3 DMA Active Cycle                                         |

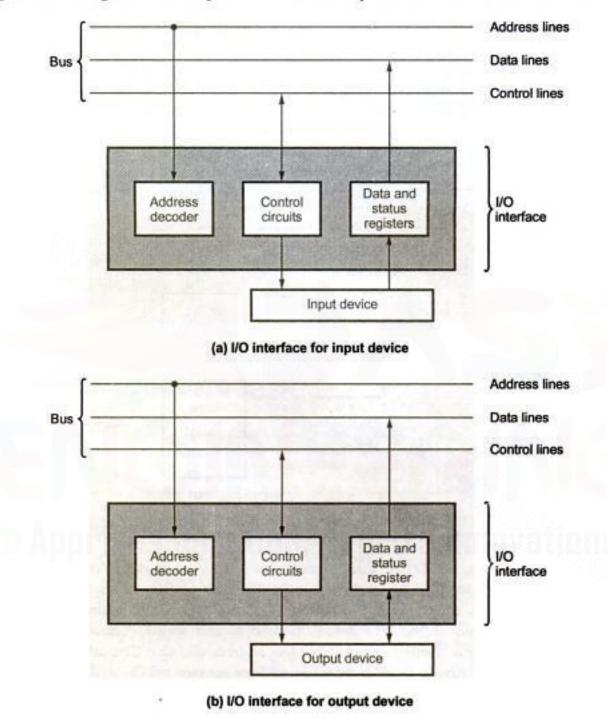

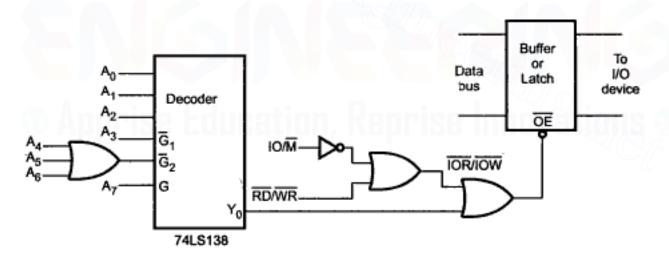

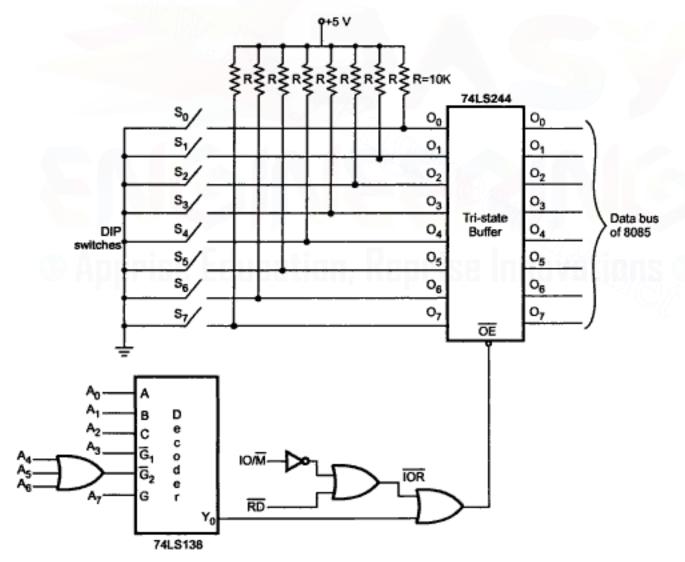

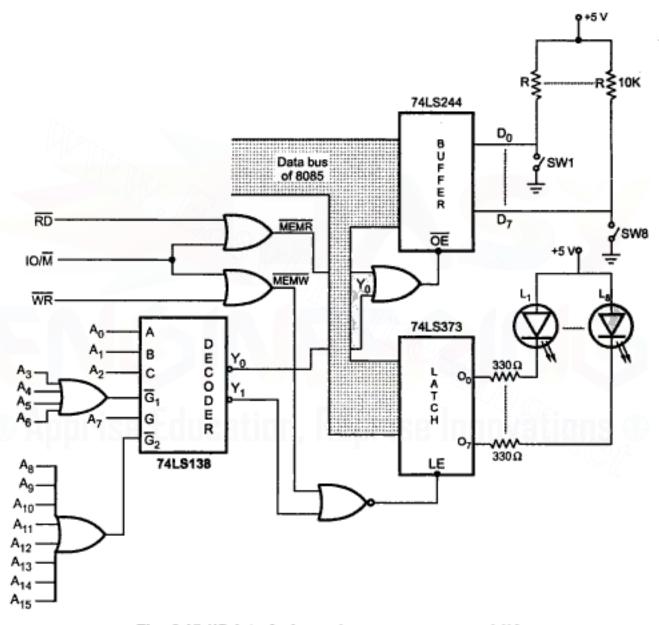

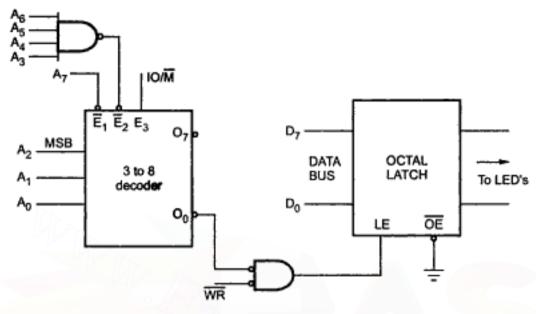

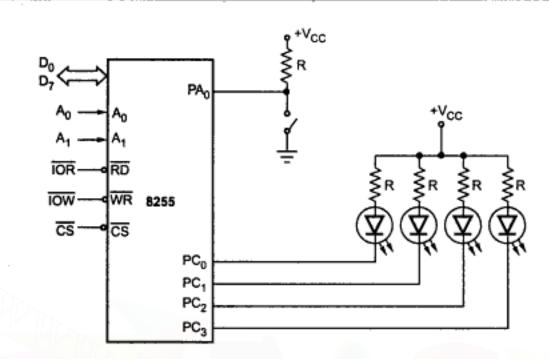

| 6.3 I/O Interfacing Techniques in 8085                           |

| 6.3.1 I/O Mapped I/O                                             |

| 6.3.2 I/O Device Selection                                       |

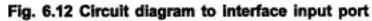

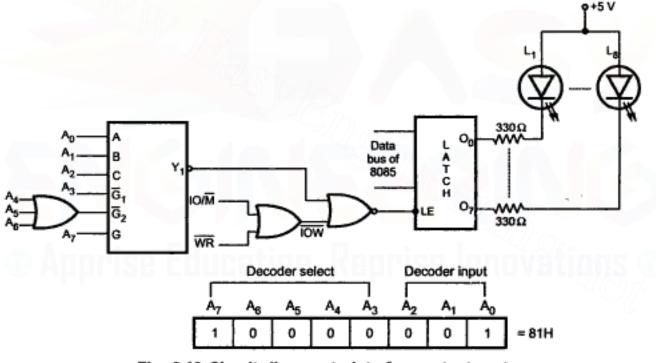

| 6.3.3 Interfacing Input and Output Devices with Examples         |

| 6.3.4 Memory Mapped I/O 6 - 21                                   |

| 6.3.5 Comparison between I/O Mapped I/O and Memory Mapped I/O    |

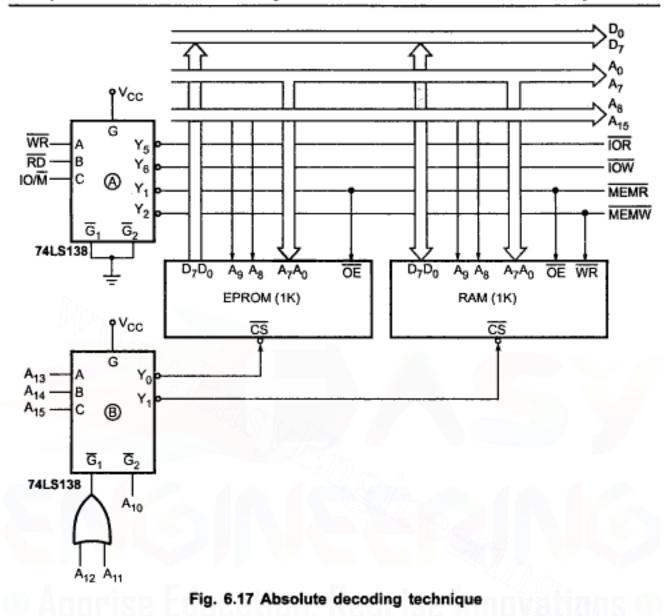

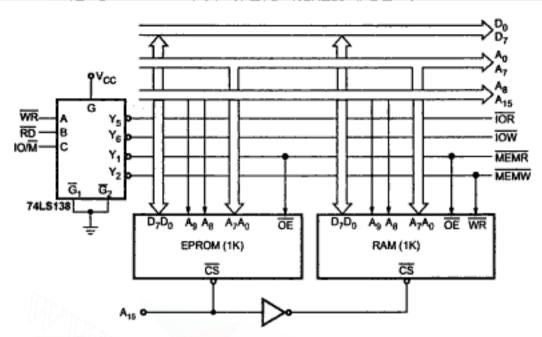

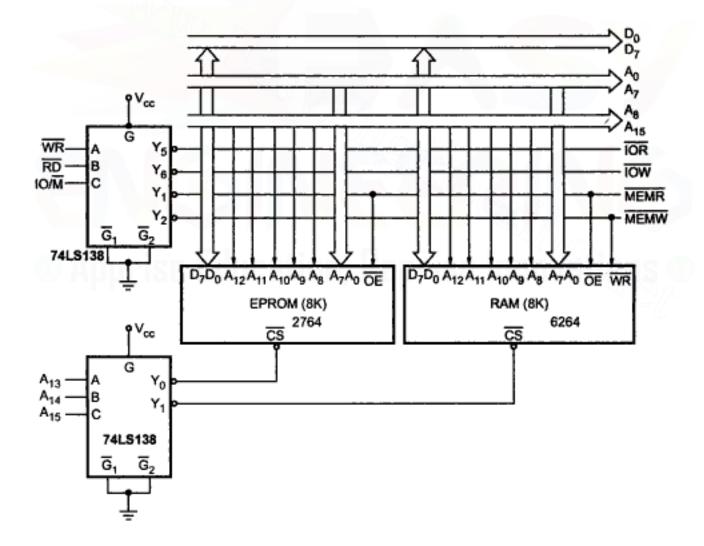

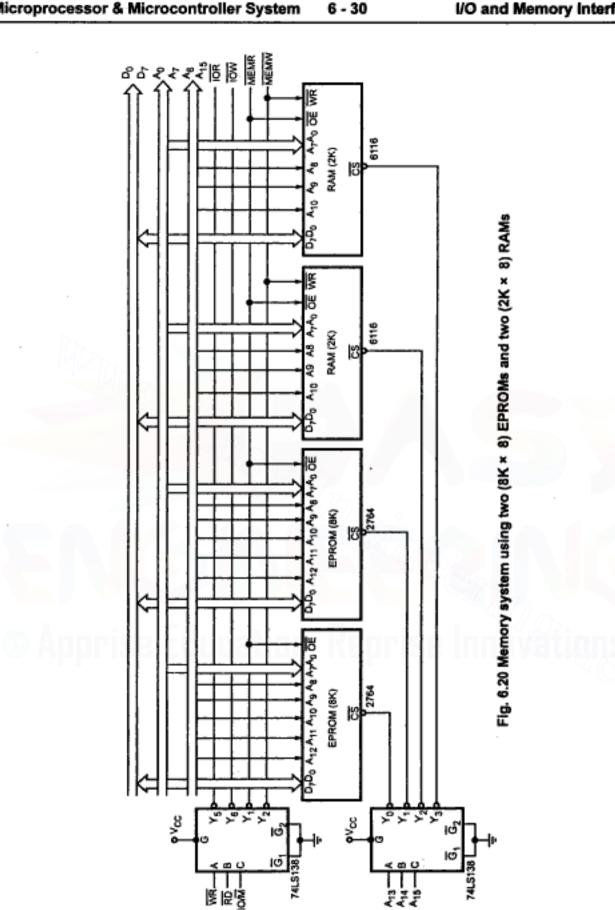

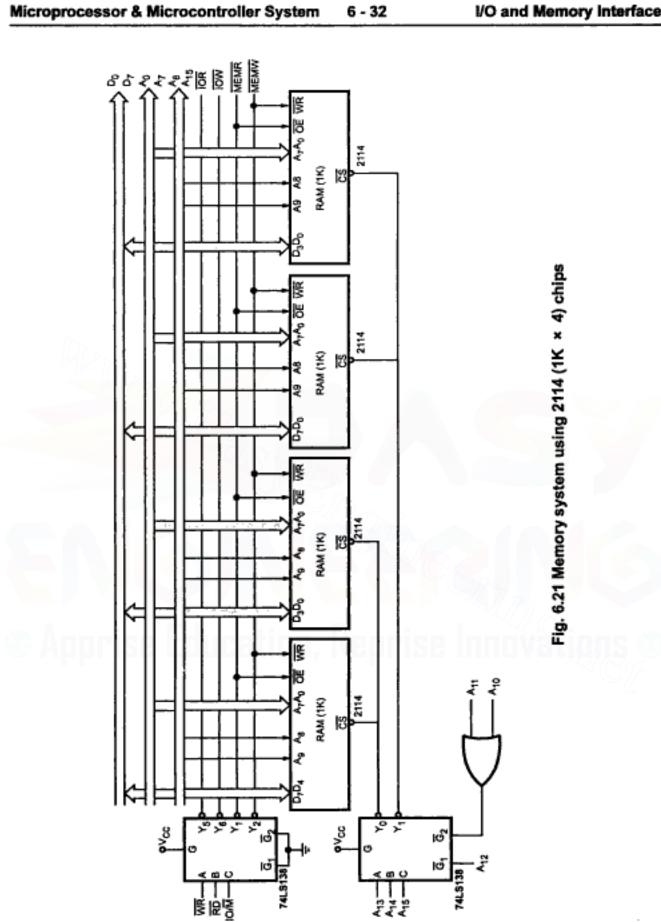

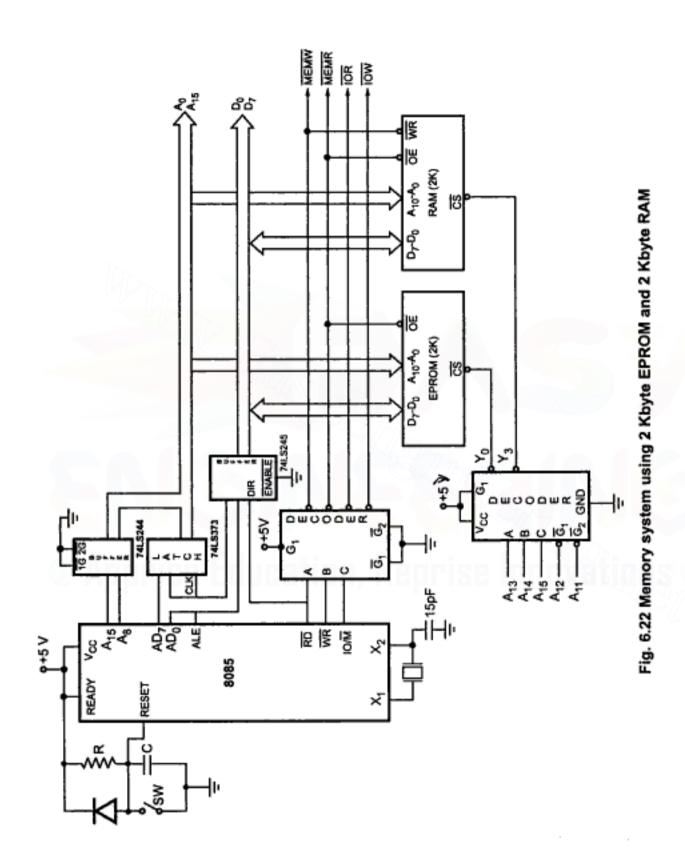

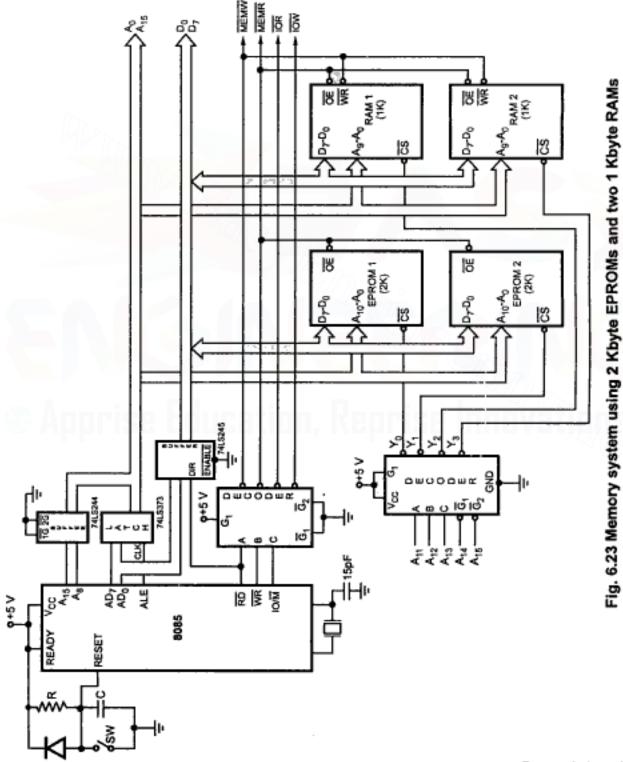

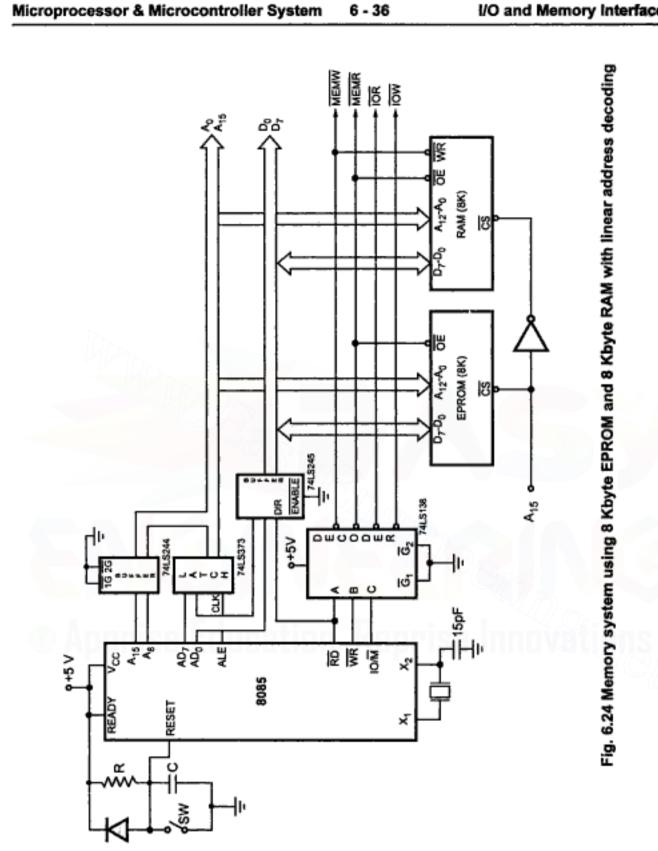

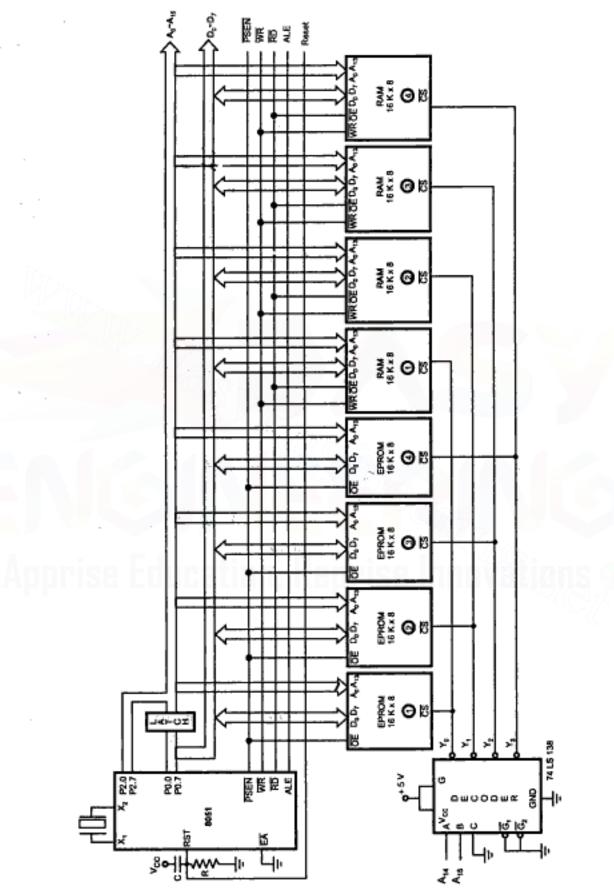

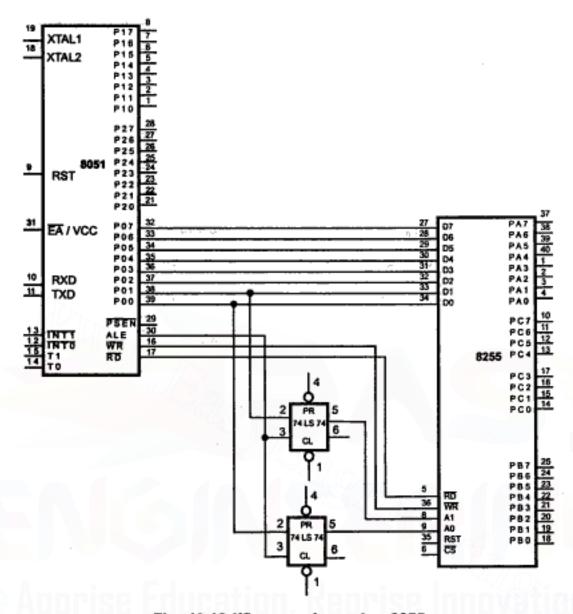

| 6.4 Memory Interfacing                                           |

| 6.4.1 Basic Concepts in Memory Interfacing                       |

| 6.4.2 Interfacing Examples                                       |

|                                                                  |

| Chapter-7 Microcontroller 8051 (7 - 1) to (7 - 38)               |

| 7.1 Introduction                                                 |

| 7.2 Features of 8051                                             |

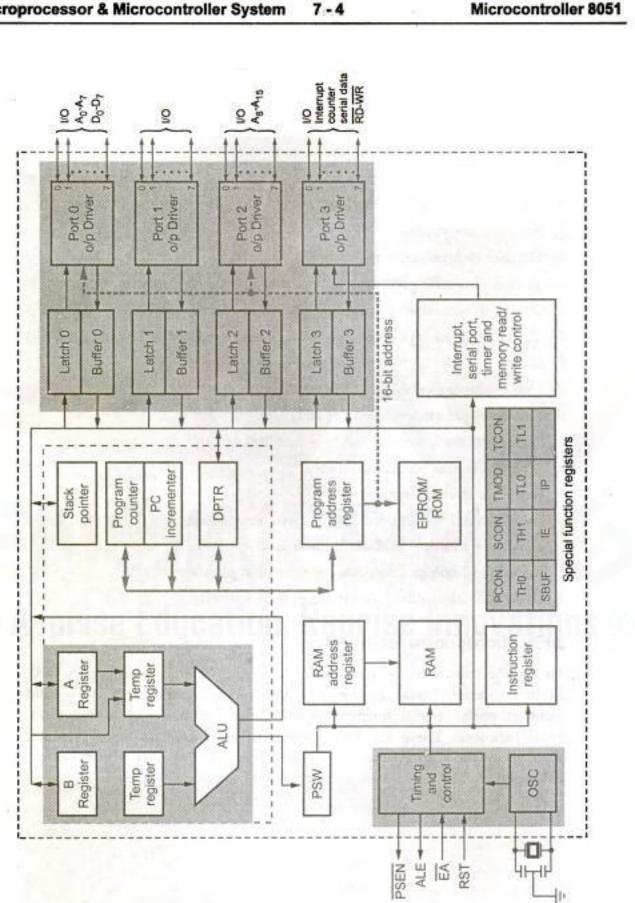

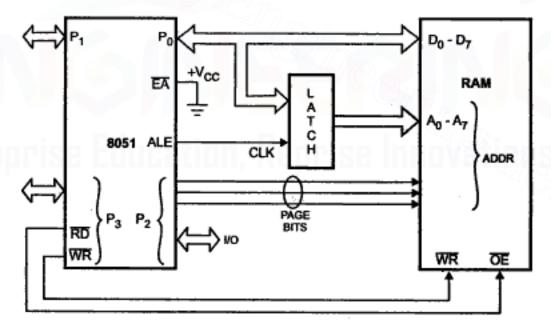

| 7.3 8051 Microcontroller Hardware                                |

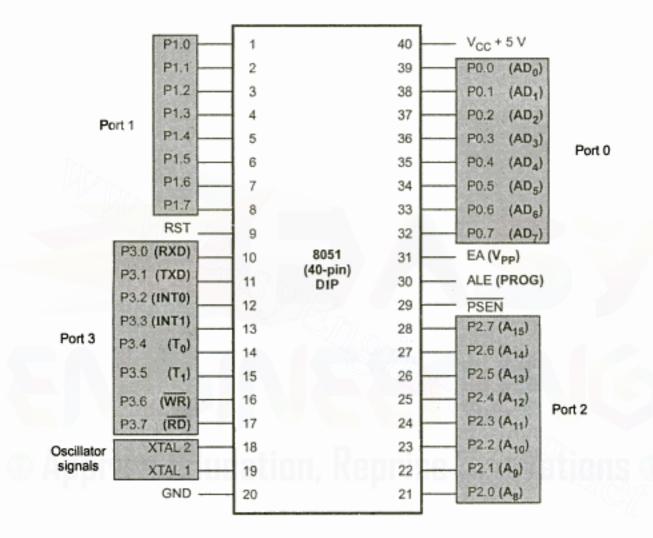

| 7.3.1 Pin-out of 8051                                            |

| 7.3.2 Central Processing Unit (CPU)                              |

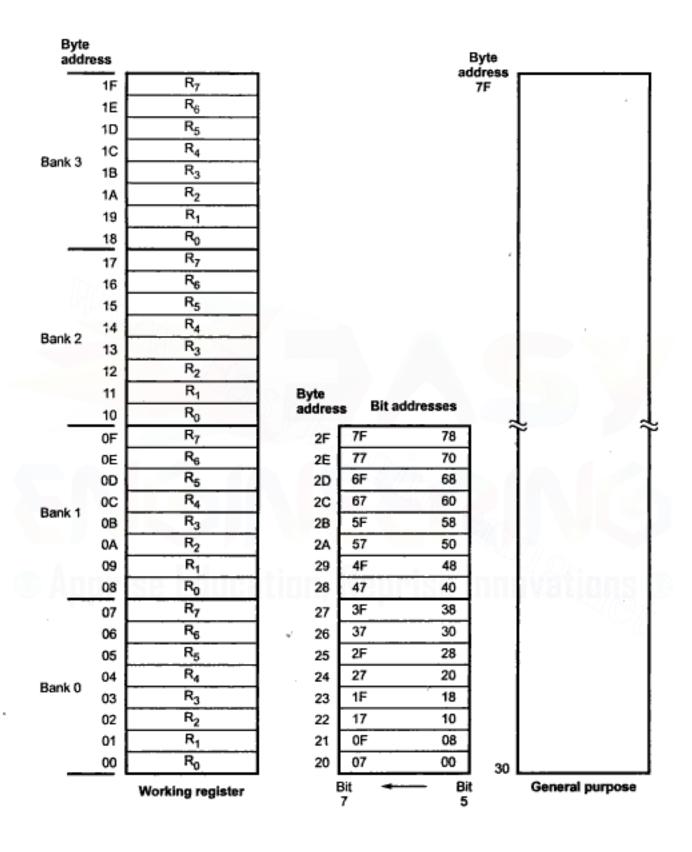

| 7.3.3 Internal RAM                                               |

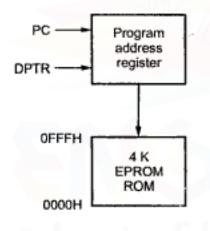

| 7.3.4 Internal ROM                                               |

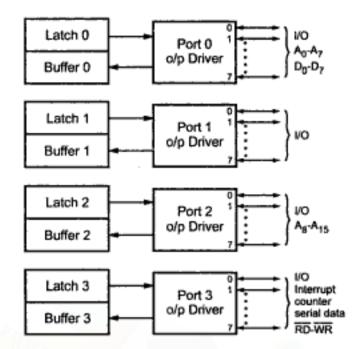

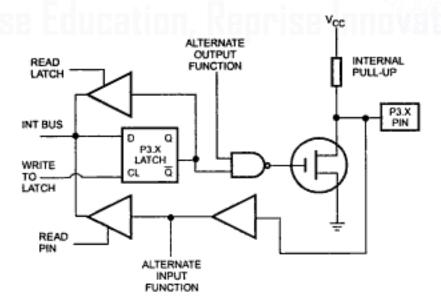

| 7.3.5 Input/Output Ports                                         |

| 7.3.6 Register Set of 8051 7 - 10                                |

(viii)

200

į

#### Downloaded From : www.EasyEngineering.net

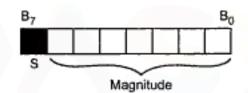

| 7,3.6.1 Register A (Accumulator)                                      |

|-----------------------------------------------------------------------|

| 7.3.6.2 Register B                                                    |

| 7.3.6.3 Program Status Word (Flag Register)                           |

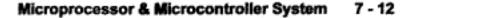

| 7.3.6.4 Stack and Stack Pointer                                       |

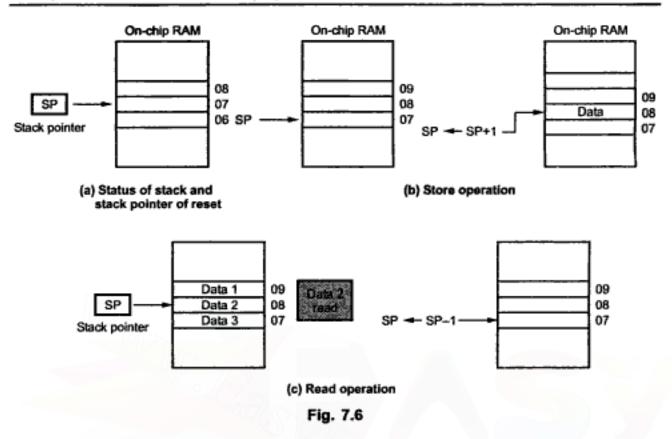

| 7.3.6.5 Data Pointer (DPTR)                                           |

| 7.3.6.6 Program Counter                                               |

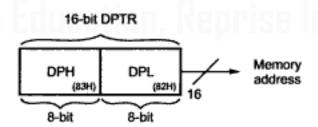

| 7.3.6.7 Special Function Registers                                    |

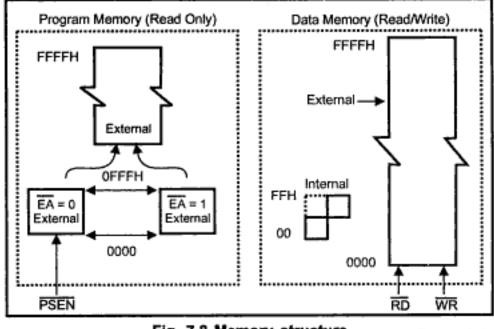

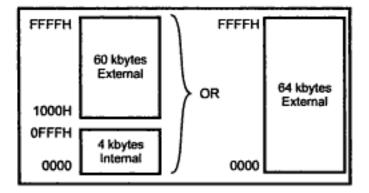

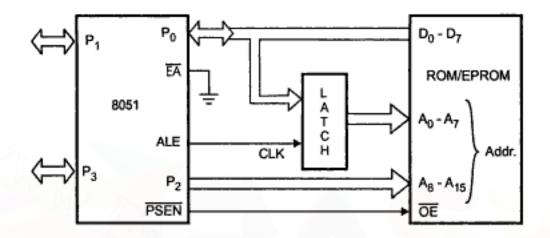

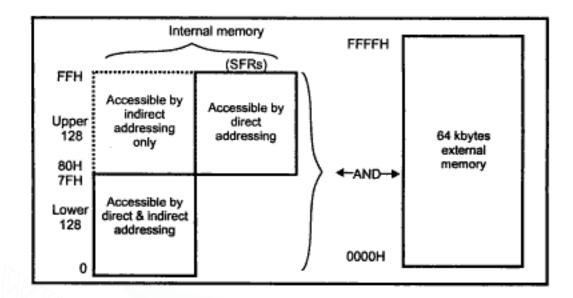

| 7.4 Memory Organization in 8051 7 - 15                                |

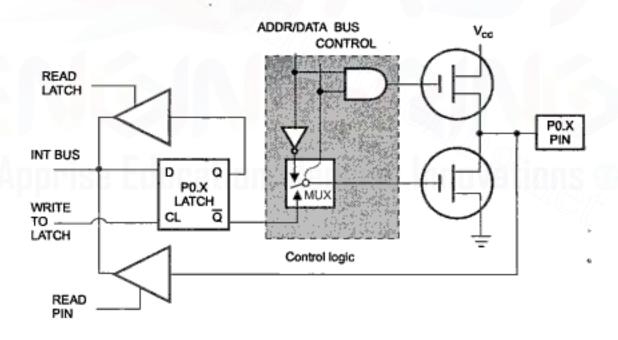

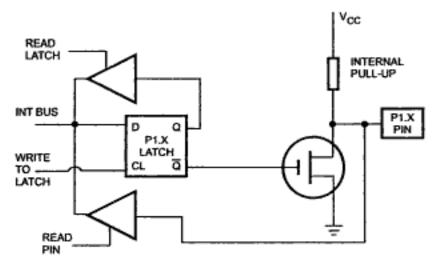

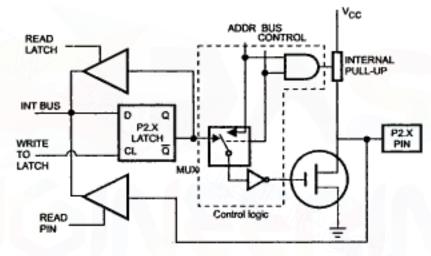

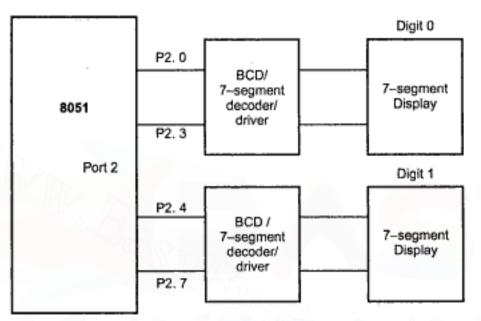

| 7.5 Input/Output Pins, Ports and Circuits                             |

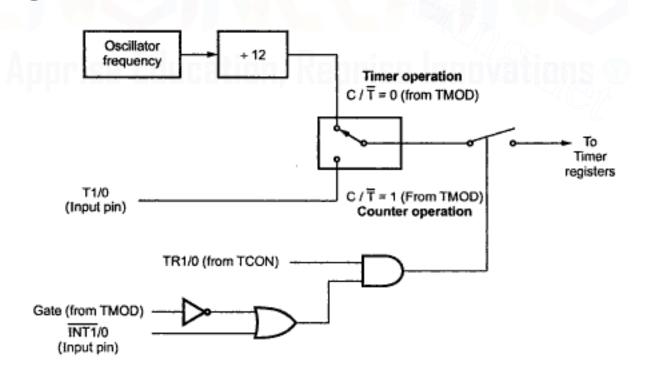

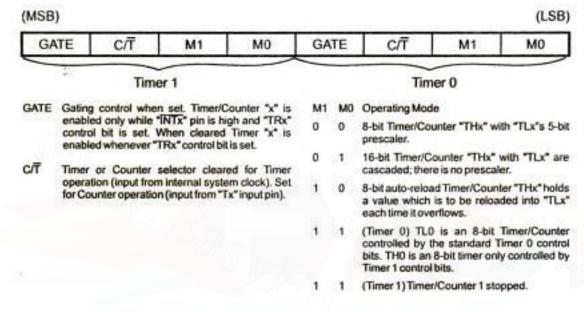

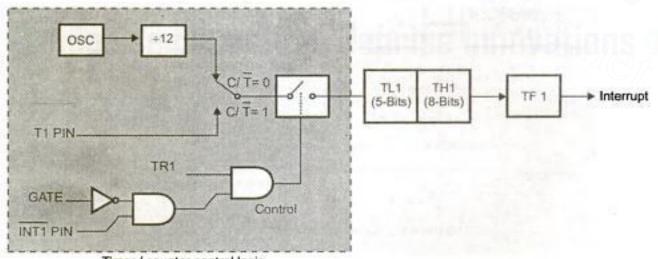

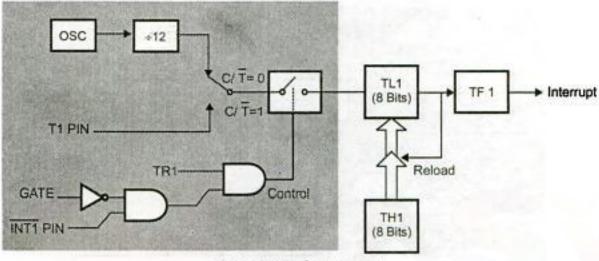

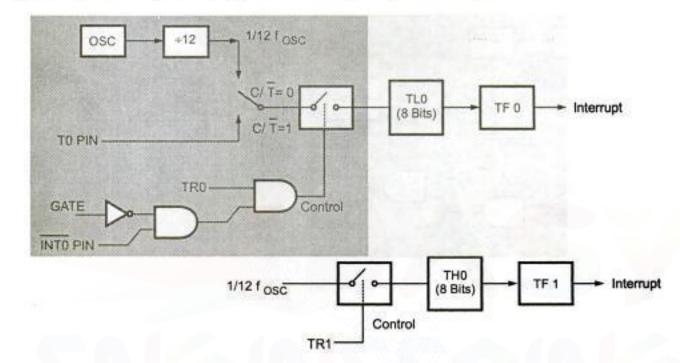

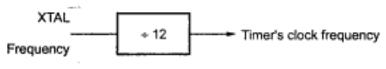

| 7.6 Timers and Counters 7 - 19                                        |

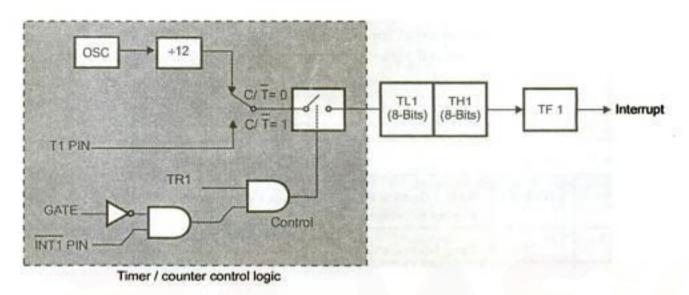

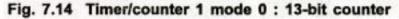

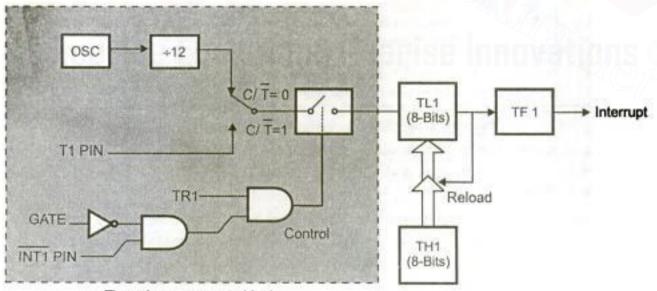

| 7.6.1 Timer/Counter Control Logic                                     |

| 7.6.2 Timer 0 and Timer 1                                             |

| 7.7 Serial Port                                                       |

| 7.7.1 Operating Modes for Serial Port                                 |

| 7.7.2 Serial Port Control Register 7 - 26                             |

| 7.7.3 Generating Baud Rates                                           |

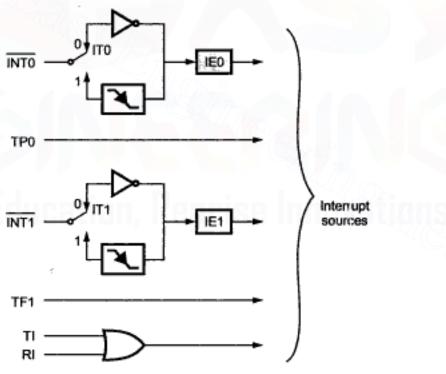

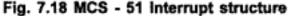

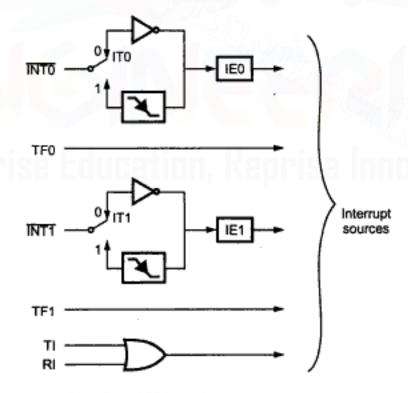

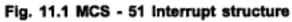

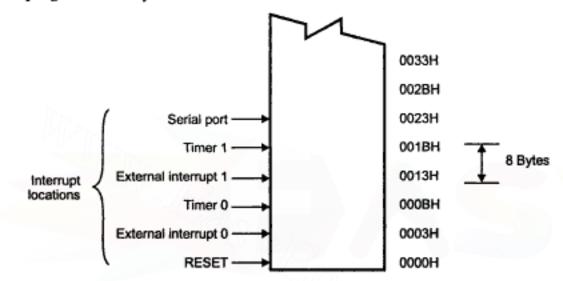

| 7.8 Interrupt Structure                                               |

| 7.8.1 Priority Level Structure                                        |

| 7.8.2 External Interrupts                                             |

| 7.8.3 Single-Step Operation                                           |

|                                                                       |

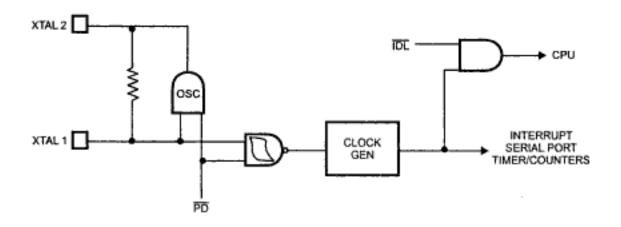

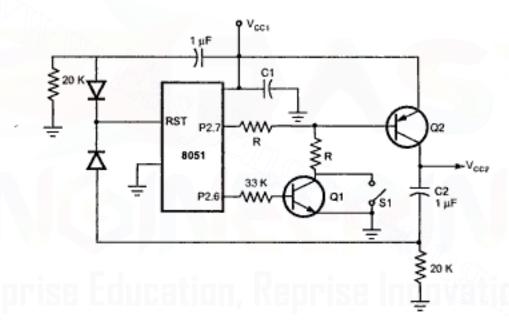

| 7.10 Power Saving Options                                             |

| 7.10.2 Power Down Mode                                                |

| 7.11 Multiprocessor Communication in MCS-51                           |

| Review Questions                                                      |

|                                                                       |

| Chapter-8 Instruction Set and Programming of 8051 (8 - 1) to (8 - 88) |

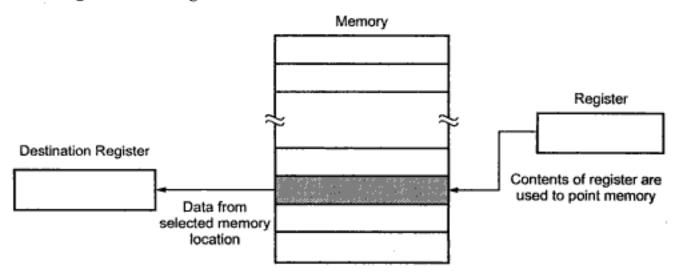

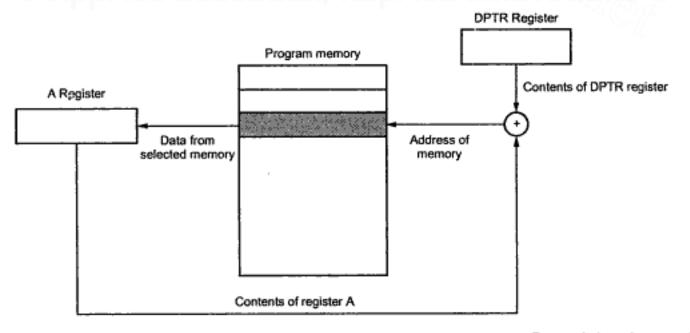

| 8.1 Addressing Modes8 - 1                                             |

| 8.2 Data Moving (Data Transfer) Instructions8 - 4                     |

| 8.2.1 Instructions to Access External Data Memory                     |

| 8.2.2 Instructions to Access External ROM / Program Memory            |

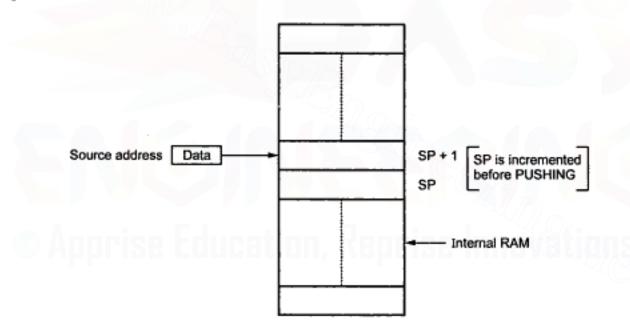

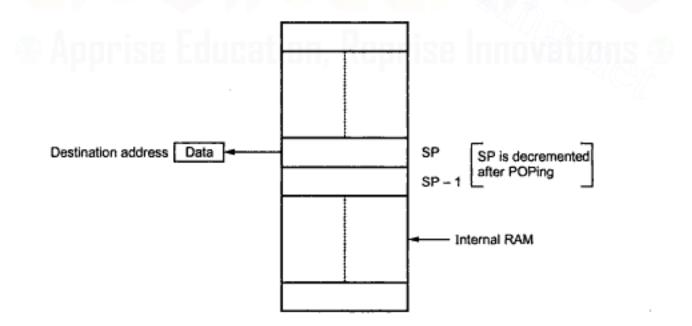

| 8.2.3 PUSH and POP Instructions                                       |

| 8.2.3.1 PUSH                                                          |

| 8.2.3.2 POP                                                           |

| 8.2.4 Data Exchange Instructions                                      |

| 8.3 Logical Instructions8 - 18                                        |

and the second second

' |

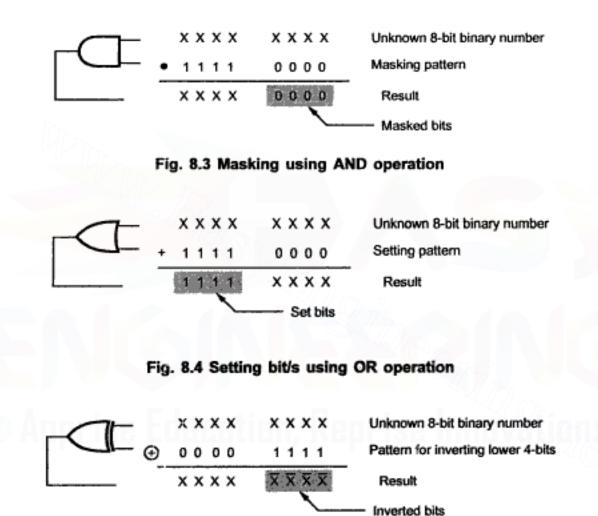

|                     | 8.3.1 Byte Level Logical Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                     | 8.3.2 Bit Level Logical Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

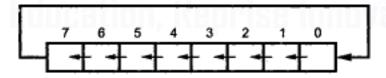

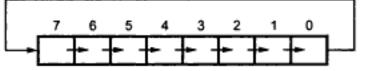

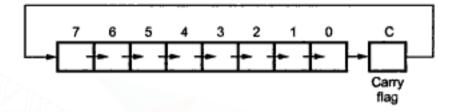

|                     | 8.3.3 Rotate and Swap Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 8.4                 | Arithmetic Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                     | 8.4.1 Flags                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                     | 8.4.2 Incrementing and Decrementing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 1                   | 8.4.3 Addition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                     | 8.4.4 Subtraction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                     | 8.4.5 Multiplication and Division                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

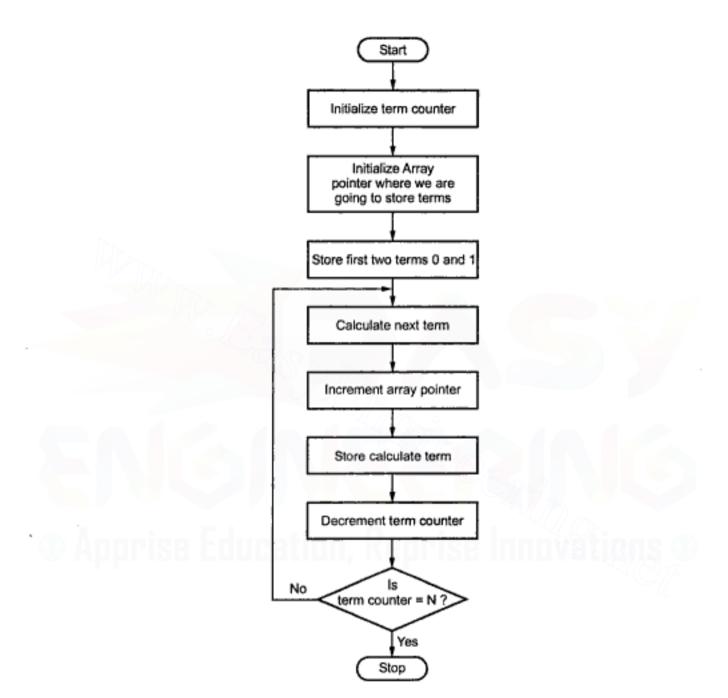

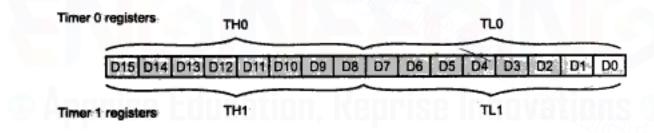

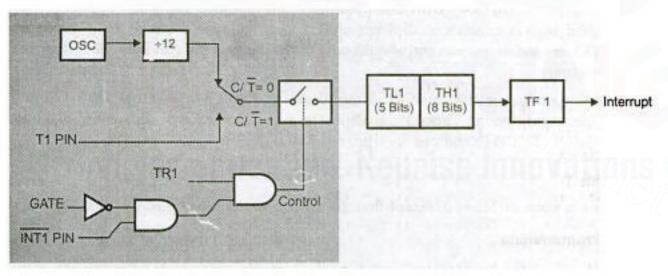

|                     | 8.4.6 Decimal Arithmetic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |