# Computer Aided Design of Micro- and Nanoelectronic Devices

### Chinmay Kumar Maiti

World Scientific

## Computer Aided Design of Micro- and Nanoelectronic Devices

This page intentionally left blank

# Computer Aided Design of Micro- and Nanoelectronic Devices

Chinmay Kumar Maiti

Siksha 'O' Anusandhan University, India

υ

New JERSEY · LONDON · SINGAPORE · BEIJING · SHANGHAI · HONG KONG · TAIPEI · CHENNAI · TOKYO www.TechnicalBooksPDF.com

#### Published by

World Scientific Publishing Co. Pte. Ltd.

5 Toh Tuck Link, Singapore 596224

USA office: 27 Warren Street, Suite 401-402, Hackensack, NJ 07601

UK office: 57 Shelton Street, Covent Garden, London WC2H 9HE

#### Library of Congress Cataloging-in-Publication Data

Names: Maiti, C. K., author.

Title: Computer aided design of micro- and nanoelectronic devices / Chinmay Kumar Maiti, Siksha 'O' Anusandhan University, India.

Description: [Hackensack] New Jersey : World Scientific, [2016] | Includes bibliographical references and index.

Identifiers: LCCN 2016015379 | ISBN 9789814713078 (hc : alk. paper)

Subjects: LCSH: Electronic apparatus and appliances--Computer-aided design. | Nanoelectromechanical systems--Design.

Classification: LCC TK7870 .M314 2016 | DDC 621.3810285--dc23 LC record available at https://lccn.loc.gov/2016015379

#### **British Library Cataloguing-in-Publication Data**

A catalogue record for this book is available from the British Library.

#### Copyright © 2017 by World Scientific Publishing Co. Pte. Ltd.

All rights reserved. This book, or parts thereof, may not be reproduced in any form or by any means, electronic or mechanical, including photocopying, recording or any information storage and retrieval system now known or to be invented, without written permission from the publisher.

For photocopying of material in this volume, please pay a copying fee through the Copyright Clearance Center, Inc., 222 Rosewood Drive, Danvers, MA 01923, USA. In this case permission to photocopy is not required from the publisher.

Desk Editor: V. Vishnu Mohan

Typeset by Stallion Press Email: enquiries@stallionpress.com

Printed in Singapore

υ

#### www.TechnicalBooksPDF.com

## Dedication

In the loving memory of

Srimati Santilata Maiti

and

Srimati Bina Das

v

This page intentionally left blank

### Preface

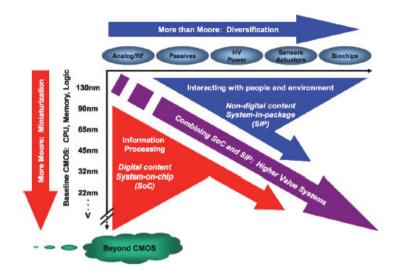

The road towards enhancing the performance of integrated circuits comprises fundamental improvement of the devices via new structures, scaling the size and transistor features which increase its speed and reduce power consumption. Combination of new device architectures and use of strain-engineered materials have led towards nanoelectronic devices and pushed the limits of CMOS and BiCMOS scaling. Typical transistor gate lengths have reached 10 nm. The first processor built with the 14 nm technology is the Intel Core-M processor. At the beginning of 2015, the fifth generation Intel Core processor was released, which is also built with the 14 nm technology and with 1.3 billion transistors.

Computer aided design and simulation of transistors for upcoming technology nodes are the main focus of this book. The monograph address mainly the design issues of advanced CMOS and bipolar devices with technical depth and conceptual clarity and presents leading-edge device design solutions to address the new challenges presented by advanced technology nodes. The device design examples covered in this monograph are in use and provide useful technology and device physics insights. The purpose of this monograph is also to bring into one resource presenting a comprehensive perspective of advanced micro- and nanoelectronic device design using advanced simulation tools.

One major limitation of currently available books in related areas is that mostly the design and simulation results presented are using 2D simulators. Due to ultra-small size of the state-of-the-art devices, 3D effects have become dominant. In order to achieve a better understanding of simulated and fabricated device characteristics, 3D process/device simulation is essential. Also 3D integration has become one of the main directions to fit into device performance roadmaps.

υ

vii

After a brief discussion on the basic device physics, the readers are introduced to device design and simulation. Device design examples considered are from various areas, viz., bipolar and CMOS technology, memory and power devices, and solar cells. This monograph also presents design, simulation and analysis of heterostructure silicon and III-V compound semiconductor devices. Detailed and extensive technology CAD simulations have been presented for stress- and strainengineered 3D FinFET devices. This monograph attempts to fill the gap in the literature in a rapidly evolving field as it blends together a wide ranging description of TCAD activities in process design to device design to compact model generation in Si, SiGe and III-V materials, technology, and their applications.

This monograph is primarily intended for senior undergraduate and graduate students and professors who wish to find a technology CAD teaching reference book and others who are interested in learning about semiconductor device design using simulation. This monograph may be used as a reference for engineers involved in advanced device and process design. Technology CAD specialists may find this monograph useful since it discusses the organization of TCAD simulation systems and also presents many case studies where the reader may apply the CAD tools in different situations. Approaches described in this monograph are expected to boost advanced device design using challenging TCAD simulations and help with characterizing new processes and devices.

I am especially grateful to all my research students whose association has been the source of learning for many new topics covered in this monograph. Special thanks go to Dr. A. Bag, who has kindly contributed a chapter (Chapter 13) on Heterojunction Solar Cells. We would also like to express our deep appreciation to WSPC team (V. Vishnu Mohan and Steven Patt). Finally, I would like to thank my family members (my wife Bhaswati, sons Ananda and Anindya) for their support, patience and understanding during the preparation of the manuscript.

> C. K. Maiti SOA University, Bhubaneswar December 2015

## **List of Tables**

| Table 1.1. Scaling MOSFET device and circuit parameters                                        | 2     |

|------------------------------------------------------------------------------------------------|-------|

| Table 6.1. Material parameters of $Ga_{0.51}In_{0.49}P$ used in GaInP/GaAs HBT device          |       |

| simulations. Data source: Ioffe Physico-Technical Institute. "New                              |       |

| Semiconductor Materials Characteristics and Properties".                                       |       |

| http://www.ioffe.ru/                                                                           | . 166 |

| Table 6.2. Material properties for $Ga_{0.51}In_{0.49}P$ and GaAs. Data source: Ioffe          |       |

| Physico-Technical Institute. "New Semiconductor Materials                                      |       |

| Characteristics and Properties". http://www.ioffe.ru/                                          | . 167 |

| Table 6.3. Structure of GaInP/GaAs collector-up HBT used in simulation. Data                   |       |

| source: Ioffe Physico-Technical Institute. "New Semiconductor                                  |       |

| Materials Characteristics and Properties". http://www.ioffe.ru/                                | . 169 |

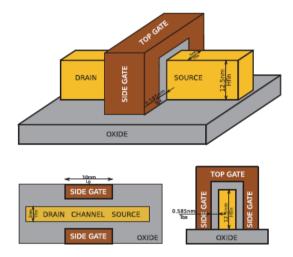

| Table 8.1. n-FinFET model geometry parameters. After B. Gaynor, Simulation of                  |       |

| FinFET electrical performance dependence on Fin shape and TSV and                              |       |

| back-gate noise coupling in 3D integrated circuits, PhD Thesis, Tufts                          |       |

| University, 2014.                                                                              | . 226 |

| Table 8.2. The FinFET parameters used in simulation                                            | . 236 |

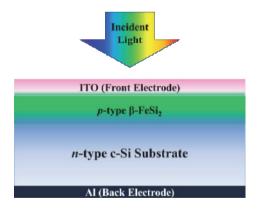

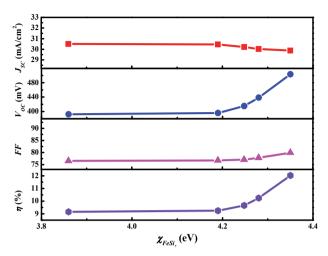

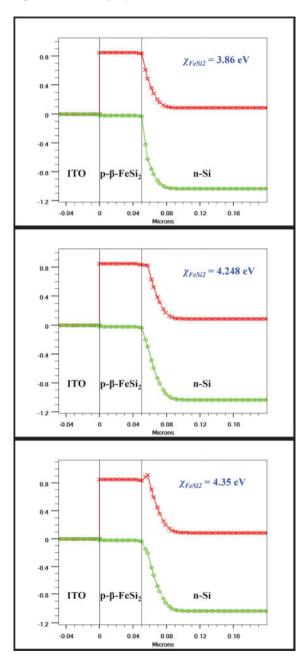

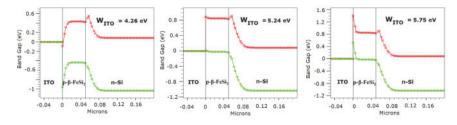

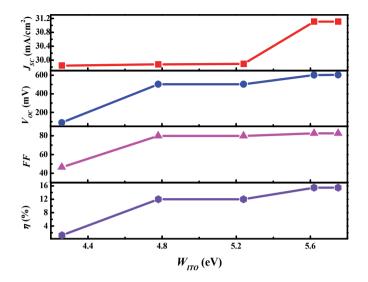

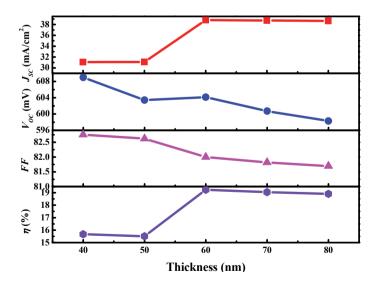

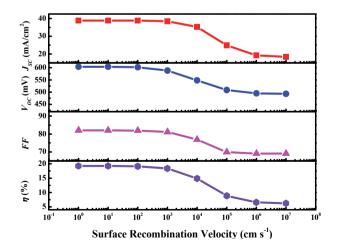

| Table 13.1. Material parameters and device dimensions of $\beta\text{-FeSi}_2$ and c-Si layer. |       |

| Data source: Ioffe Physico-Technical Institute. "New Semiconductor                             |       |

| Materials Characteristics and Properties". http://www.ioffe.ru/                                | . 377 |

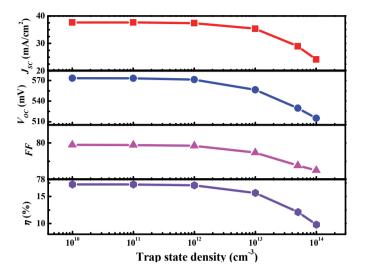

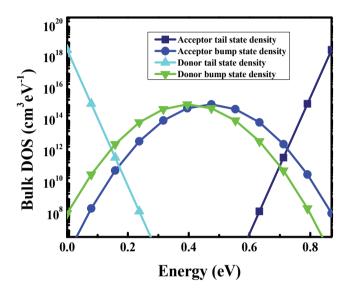

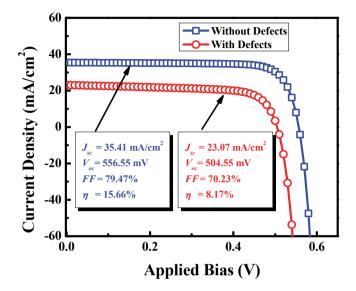

| Table 13.2. Parameters for defects modeling in amorphous FeSi <sub>2</sub> . Data source:      |       |

| Ioffe Physico-Technical Institute. "New Semiconductor Materials                                |       |

| Characteristics and Properties". http://www.ioffe.ru/                                          | . 379 |

| Table 13.3. Parameters for defects modeling at FeSi <sub>2</sub> /Si interface. Data source:   |       |

| Ioffe Physico-Technical Institute. "New Semiconductor Materials                                |       |

| Characteristics and Properties". http://www.ioffe.ru/                                          | . 380 |

| Table 14.1. Locally extracted parameters                                                       | . 418 |

ix

D

This page intentionally left blank

## **List of Figures**

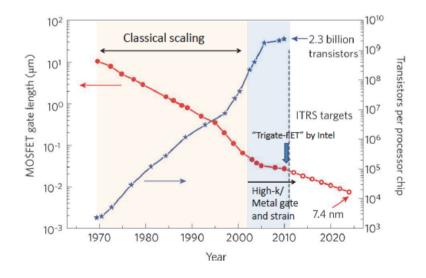

| Figure 1.1. Time evolution of MOSFET gate length in microprocessors. ITRS roadmap projections show the gate length to scale down to around 8nm at |    |

|---------------------------------------------------------------------------------------------------------------------------------------------------|----|

|                                                                                                                                                   |    |

| the end-of-roadmap. After V. Deshpande, Scaling beyond Moore: single                                                                              |    |

| electron transistor and single atom transistor integration on CMOS, PhD                                                                           | ~  |

| Thesis, University of Grenoble, 2012.                                                                                                             | 3  |

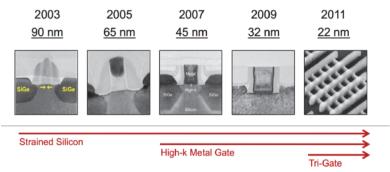

| Figure 1.2. Recent MOSFET architectures and process nodes released by Intel                                                                       |    |

| Corporation. After M. Koyama, Electrical characterization of interface                                                                            |    |

| properties in nano-scaled MOSFET devices based on low-frequency                                                                                   |    |

| fluctuations, PhD Thesis, Universite Grenoble Alpes, 2015                                                                                         | 6  |

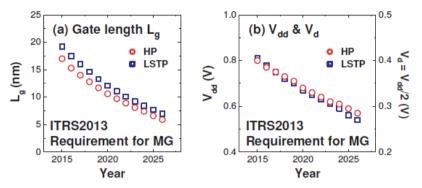

| Figure 1.3. ITRS requirements for future high performance (HP) and low standby                                                                    |    |

| power (LSTP) logic circuits consisting of MG FETs. (a) MOSFET gate                                                                                |    |

| length Lg, and (b) circuit supply voltage Vd and MOSFET drain voltage                                                                             |    |

| Vd are plotted as a function of year between 2015 and 2026 (Source:                                                                               |    |

| ITRS 2013)                                                                                                                                        | 7  |

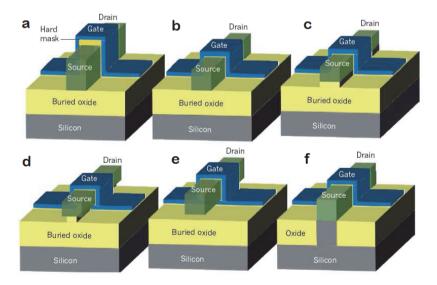

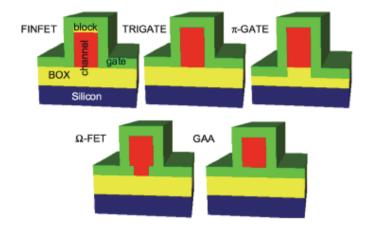

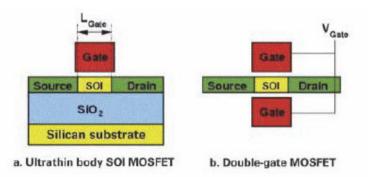

| Figure 1.4. Types of multiple gate MOSFETs. (a) SOI DG FinFET, (b) SOI tri-gate                                                                   |    |

| FET, (c) SOI $\pi$ -gate FET, (d) SOI $\Omega$ -gate FET, (d) SOI quadruple-GAA                                                                   |    |

| FET, and (e) bulk tri-gate FET. After M. Koyama, Electrical                                                                                       |    |

| characterization of interface properties in nano-scaled MOSFET devices                                                                            |    |

| based on low-frequency fluctuations, PhD Thesis, Universite Grenoble                                                                              |    |

| Alpes, 2015                                                                                                                                       | 8  |

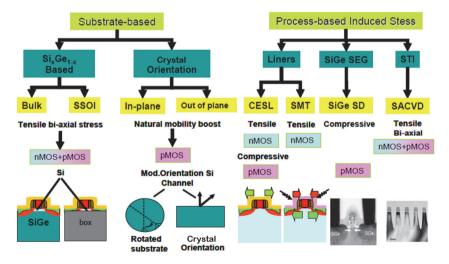

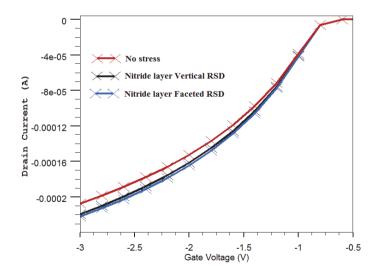

| Figure 1.5. Schemes of front end stressors types. After V. Fiori, How do Mechanics                                                                |    |

| and Thermo mechanics affect microelectronic products: Some residual                                                                               |    |

| stress and strain effects, investigations and industrial management, PhD                                                                          |    |

| Thesis, Linstitut national des sciences appliquées de Lyon, 2010                                                                                  | 10 |

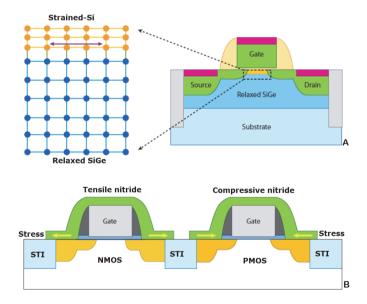

| Figure 1.6. Illustration of process-induced stress on Si MOSFETs. (a) Biaxial stress                                                              |    |

| caused from lattice mismatch between the Si channel and the relaxed SiGe                                                                          |    |

| substrate. (b) Uniaxial stress induced by the nitride capping layer. After                                                                        |    |

| M. Chu, Characterization and modeling of strained Si FET and GaN                                                                                  |    |

| HEMT devices, PhD Thesis, University of Florida, 2011                                                                                             | 11 |

|                                                                                                                                                   |    |

D

xii

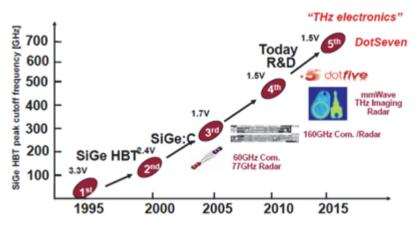

| Figure 1.7. Evolution roadmap of SiGe HBTs. Source: ITRS 2013                     | 16   |

|-----------------------------------------------------------------------------------|------|

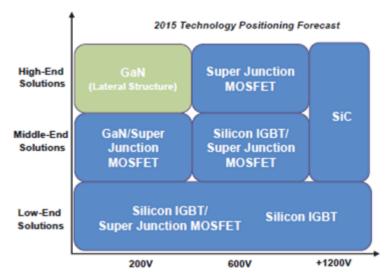

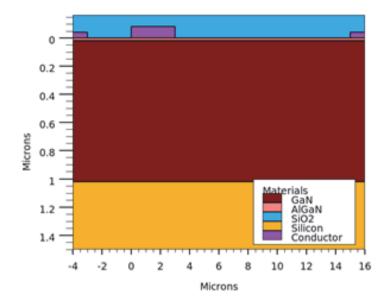

| Figure 1.8. Prediction for GaN-based technologies. After D. J. Macfarlane, Design |      |

| and fabrication of AlGaN/GaN HEMTs with high breakdown voltages,                  |      |

| PhD thesis, University of Glasgow, 2014                                           | 18   |

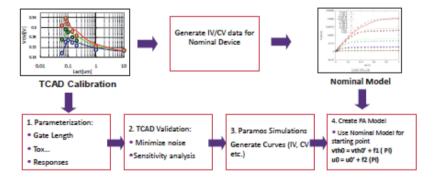

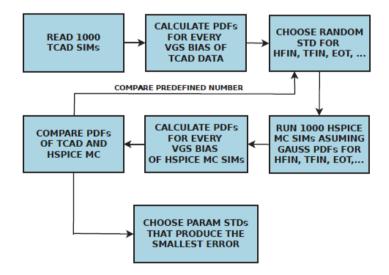

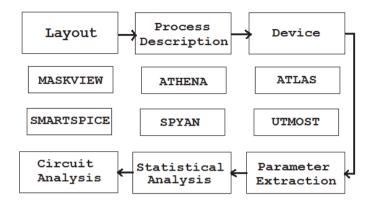

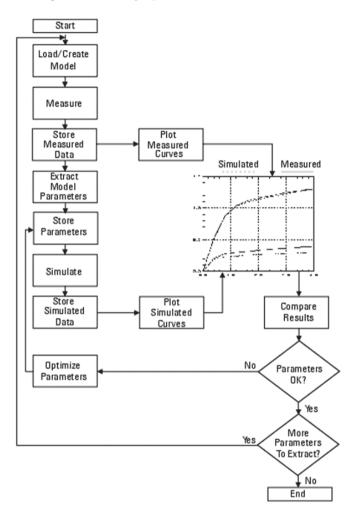

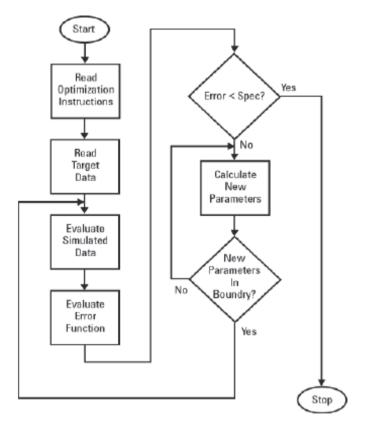

| Figure 1.9. SPICE parameter extraction procedure using TCAD. Source. Dr. T. K.    |      |

| Maiti, private communication                                                      | 20   |

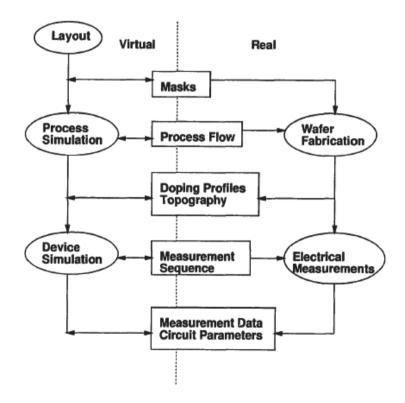

| Figure 2.1. Sentaurus TCAD flow. After P. Feng, Design, modeling and analysis of  |      |

| non-classical field effect transistors, PhD Thesis, Syracuse University,          |      |

| 2012                                                                              | 27   |

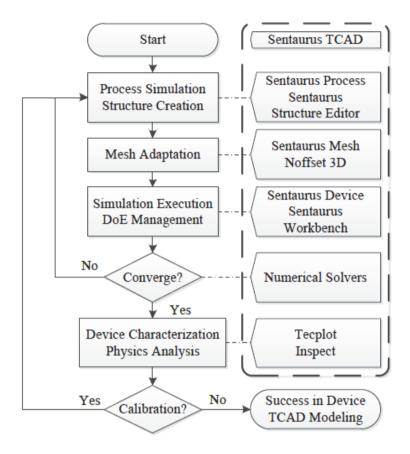

| Figure 2.2. TCAD simulation flow begins with process simulation and ends with     |      |

| electrical parameter extraction                                                   | 30   |

| Figure 2.3. Simulation setup in Sentaurus Workbench                               |      |

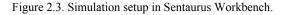

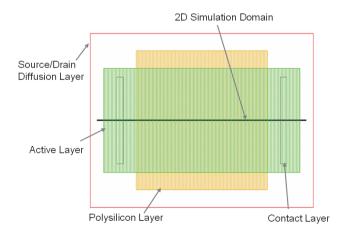

| Figure 2.4. Defining the simulation cross section in the NMOS top view            |      |

| Figure 2.5. Mesh requirements are defined differently for different areas of the  |      |

| device. An initial vertical spacing is specified followed by denser mesh          |      |

| specifications in the channel, source, drain, and LDD regions                     | 32   |

| Figure 2.6. 2D process simulation generates a full cross section of an NMOS       |      |

| transistor                                                                        | 33   |

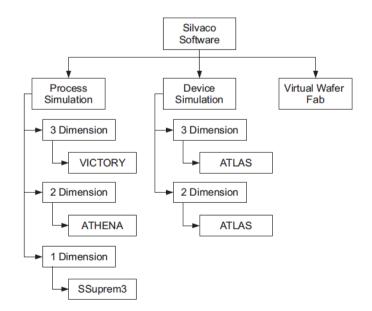

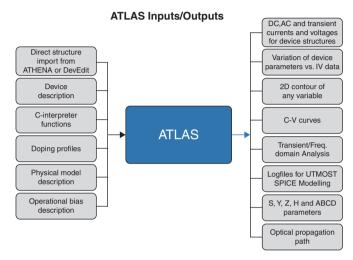

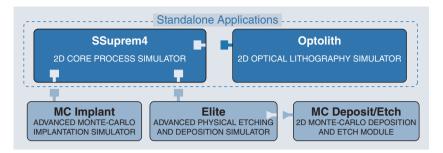

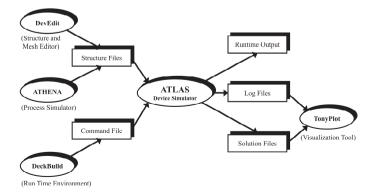

| Figure 2.7. A brief overview of SILVACO TCAD software                             |      |

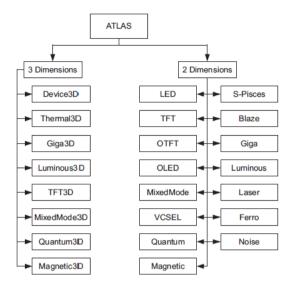

| Figure 2.8. SILVACO ATLAS framework architecture                                  |      |

| Figure 2.9. SILVACO ATLAS inputs and outputs. After W. Y. Jin, Mobility           |      |

| enhancement of nanoscale biaxial strained silicon metal-oxide                     |      |

| semiconductor field effect transistor, Master's Thesis, Universiti                |      |

| Teknologi Malaysia, 2009                                                          | 41   |

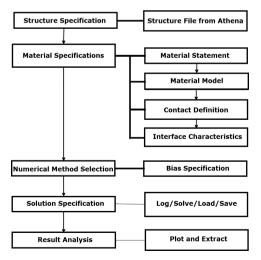

| Figure 2.10. Simulation flow diagram of SILVACO ATLAS. After W. Y. Jin,           |      |

| Mobility enhancement of nanoscale biaxial strained silicon metal-oxide            |      |

| semiconductor field effect transistor, Master's Thesis, Universiti                |      |

| Teknologi Malaysia, 2009                                                          | 41   |

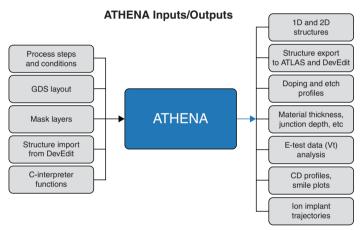

| Figure 2.11. SILVACO ATHENA framework architecture                                |      |

| Figure 2.12. SILVACO ATHENA inputs and outputs                                    |      |

| Figure 2.13. SILVACO VictoryProcess inputs and outputs                            |      |

| Figure 2.14. SILVACO VictoryDevice inputs and outputs                             |      |

| Figure 2.15. VictoryStress information flow                                       |      |

| Figure 2.16. VictoryCell input/output flow information                            |      |

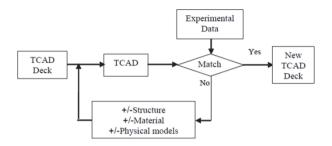

| Figure 3.1. Device design methodology. After A. Quiroga, Investigation and        |      |

| development of advanced Si/SiGe and Si/SiGeC Heterojunction Bipolar               |      |

| Transistors by means of Technology Modeling, PhD Thesis, Universite               |      |

| Paris-Sud, 2013                                                                   | 58   |

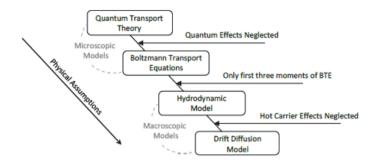

| Figure 3.2. Hierarchy overview of the semiconductor transport theories. After A.  |      |

| Quiroga, Investigation and development of advanced Si/SiGe and                    |      |

| Si/SiGeC Heterojunction Bipolar Transistors by means of Technology                |      |

|                                                                                   | . 64 |

| Modeling, PhD Thesis, Universite Paris-Sud, 2013                                  | 64   |

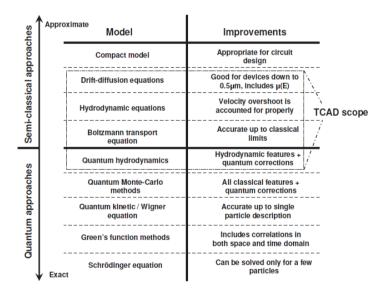

| Figure 3.3. Transport models used in device simulation. After A. N. Bhoj, Device-<br>circuit co-design approaches for multi-gate FET technologies, PhD<br>Thesis, Princeton University, 2013                                                                                                                 | 64  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

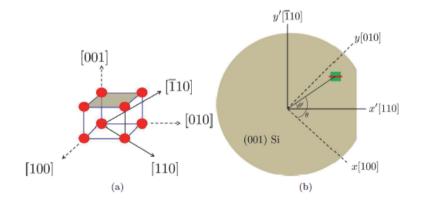

| Figure 3.4. (a) Miller indices (b) Coordinate axes in (100) Si with a wafer flat orthogonal to the [110] orientation. The transistor channel here is perpendicular to the [110] axis i.e., $\varphi' = \pi/2$ . After S. K. Marella, Performance variations due to layout-dependent stress in VLSI circuits, |     |

| PhD Thesis, University of Minnesota, 2015                                                                                                                                                                                                                                                                    | 68  |

| Figure 3.5. Method of calibration flow. After H. Ramakrishnan, Strained silicon                                                                                                                                                                                                                              | 00  |

| technology for low-power high-speed circuit applications, PhD Thesis,                                                                                                                                                                                                                                        |     |

| Newcastle University, 2008                                                                                                                                                                                                                                                                                   | 84  |

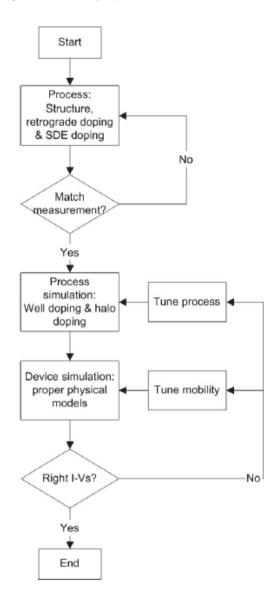

| Figure 3.6. Simplified flowchart of systematic simulation calibration methodology.                                                                                                                                                                                                                           |     |

| After X. Wang, Simulation study of scaling design, performance                                                                                                                                                                                                                                               |     |

| characterization, statistical variability and reliability of decananometer                                                                                                                                                                                                                                   |     |

| MOSFETs, PhD Thesis, University of Glasgow, 2010                                                                                                                                                                                                                                                             | 86  |

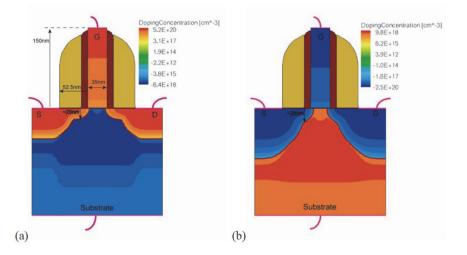

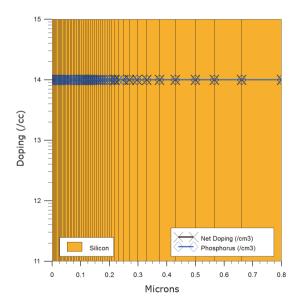

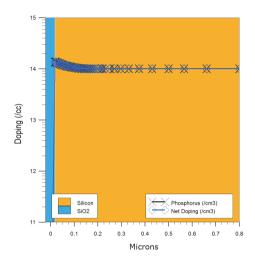

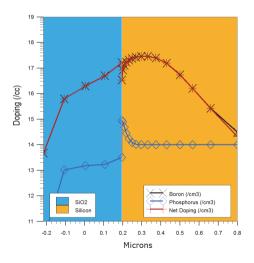

| Figure 3.7. Simulation structures of 35nm gate length n-MOSFET (a) and                                                                                                                                                                                                                                       |     |

| p-MOSFET (b) based on Toshiba experimental data. After X. Wang,                                                                                                                                                                                                                                              |     |

| Simulation study of scaling design, performance characterization,                                                                                                                                                                                                                                            |     |

| statistical variability and reliability of decananometer MOSFETs, PhD                                                                                                                                                                                                                                        | 07  |

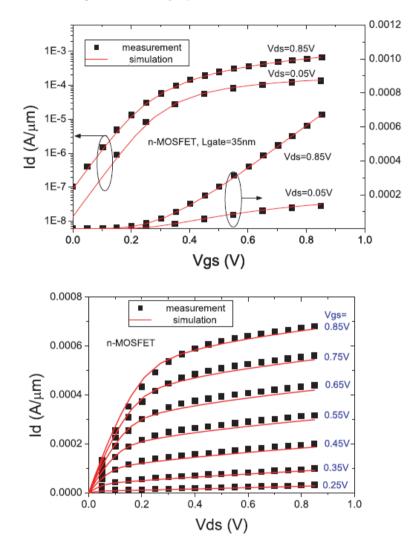

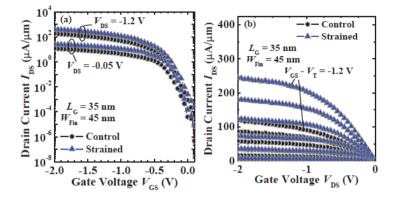

| Thesis, University of Glasgow, 2010<br>Figure 3.8. $I_d - V_g$ and $I_d - V_d$ characteristics calibrations of Toshiba 35nm gate                                                                                                                                                                             | 0/  |

| length n-channel MOSFETs with supply voltage 0.85V. After X. Wang,                                                                                                                                                                                                                                           |     |

| Simulation study of scaling design, performance characterization,                                                                                                                                                                                                                                            |     |

| statistical variability and reliability of decananometer MOSFETs, PhD                                                                                                                                                                                                                                        |     |

| Thesis, University of Glasgow, 2010                                                                                                                                                                                                                                                                          | 88  |

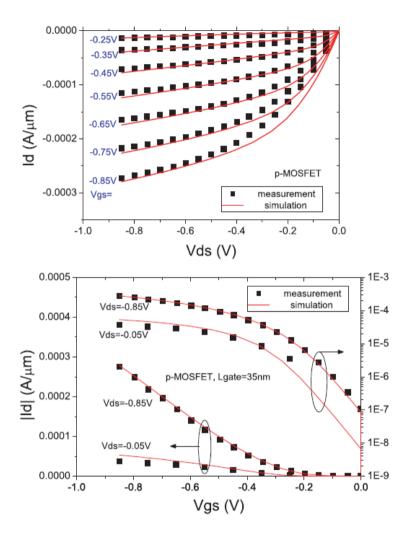

| Figure 3.9. $I_d - V_g$ and $I_d - V_d$ characteristics calibrations of Toshiba 35nm gate                                                                                                                                                                                                                    | 00  |

| length p-channel MOSFETs with supply voltage 0.85V. After X. Wang,                                                                                                                                                                                                                                           |     |

| Simulation study of scaling design, performance characterization,                                                                                                                                                                                                                                            |     |

| statistical variability and reliability of decananometer MOSFETs, PhD                                                                                                                                                                                                                                        |     |

| Thesis, University of Glasgow, 2010                                                                                                                                                                                                                                                                          | 89  |

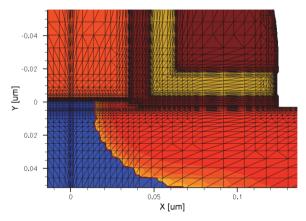

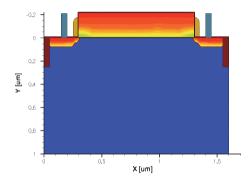

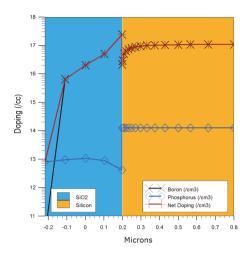

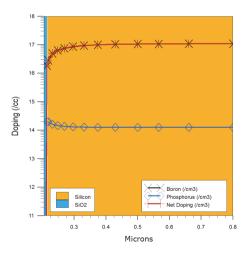

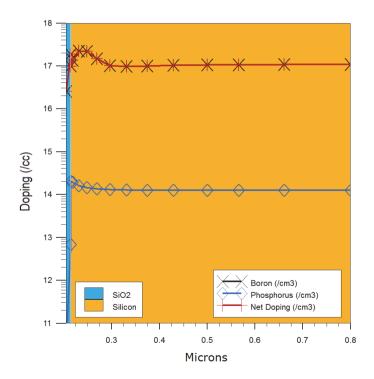

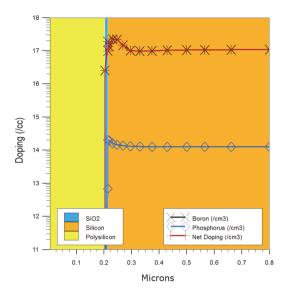

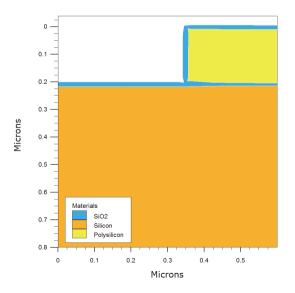

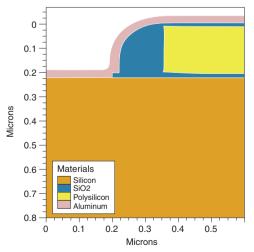

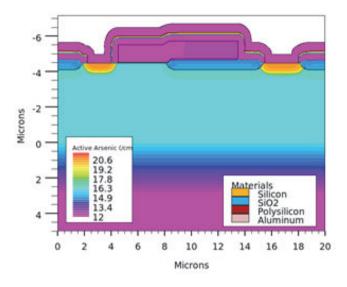

| Figure 4.1. NMOS process simulation — mesh generation                                                                                                                                                                                                                                                        |     |

| Figure 4.2. Screening oxide growth and etching                                                                                                                                                                                                                                                               | 97  |

| Figure 4.3. P-well formation and implantation                                                                                                                                                                                                                                                                | 97  |

| Figure 4.4. P-well formation: doping profile after well drive-in                                                                                                                                                                                                                                             | 98  |

| Figure 4.5. After gate oxide growth                                                                                                                                                                                                                                                                          |     |

| Figure 4.6. Threshold voltage adjustment implant                                                                                                                                                                                                                                                             |     |

| Figure 4.7. Polysilicon deposition                                                                                                                                                                                                                                                                           |     |

| Figure 4.8. Polysilicon etching and gate formation                                                                                                                                                                                                                                                           |     |

| Figure 4.9. N-channel MOSFET structure after LDD implantation                                                                                                                                                                                                                                                |     |

| Figure 4.10. LPCVD oxide deposition for spacer formation                                                                                                                                                                                                                                                     | 101 |

| Figure 4.11. N-channel MOSFET structure after heavy drain/source doping Arsenic                                                                                                                                                                                                                              |     |

| implantation                                                                                                                                                                                                                                                                                                 | 102 |

xiv

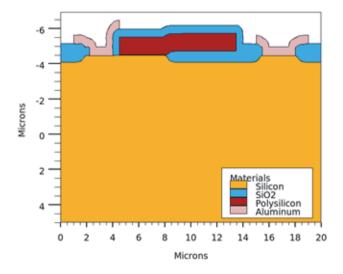

| Figure 4.12. Metal deposition                                                                    | 103 |

|--------------------------------------------------------------------------------------------------|-----|

| Figure 4.13. Contact opening                                                                     | 104 |

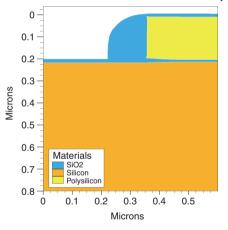

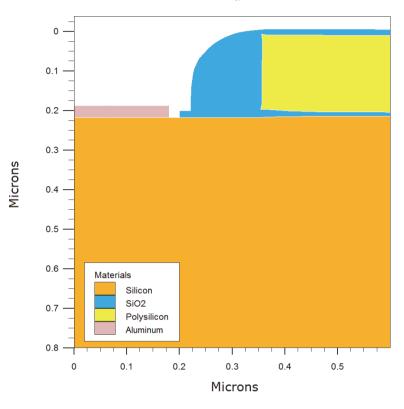

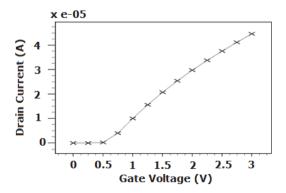

| Figure 4.14a. Full n-MOSFET device structure                                                     | 104 |

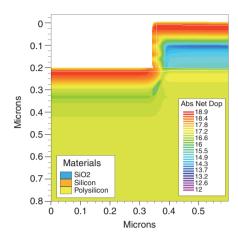

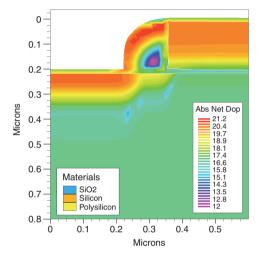

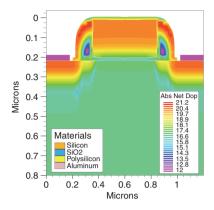

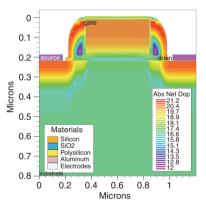

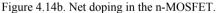

| Figure 4.14b. Net doping in the n-MOSFET                                                         | 104 |

| Figure 4.14c. Electrode specifications and grid used for the structure                           | 106 |

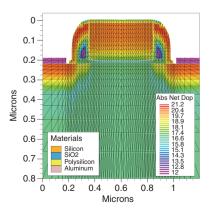

| Figure 4.15. Electrical characterization (output characteristics) using device                   |     |

| simulation tool ATLAS. Extracted device parameters are also shown                                | 106 |

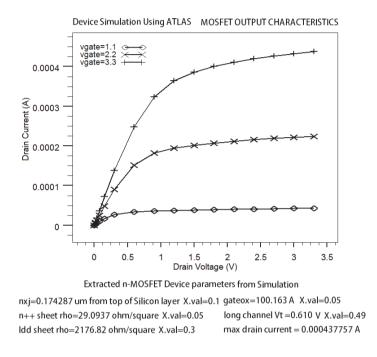

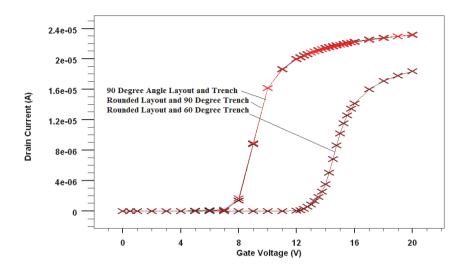

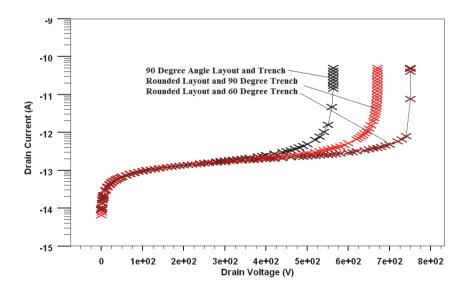

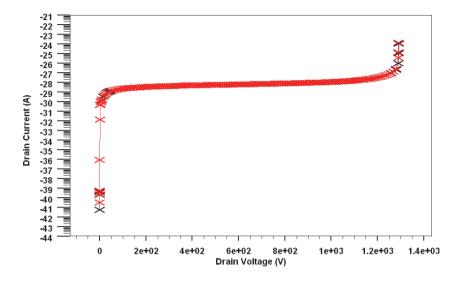

| Figure 4.16. $I_d - V_g$ characteristics simulated in ATLAS                                      | 106 |

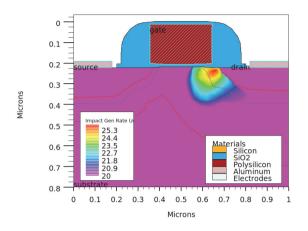

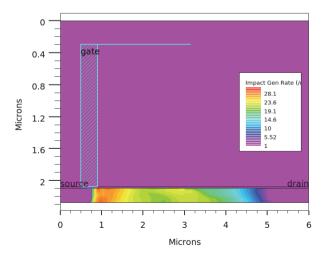

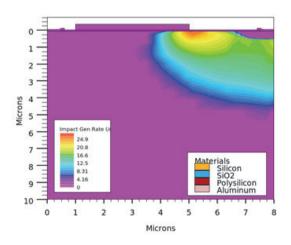

| Figure 4.17. Impact generation rate at the drain end for a drain voltage of 0.5V                 | 107 |

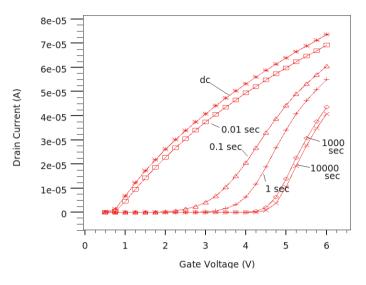

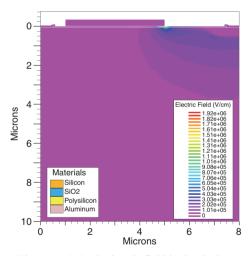

| Figure 4.18. Hot carrier reliability simulation for a p-MOSFET                                   | 109 |

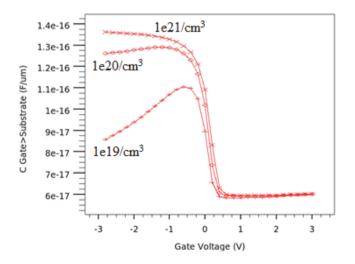

| Figure 4.19. Poly depletion effect                                                               | 110 |

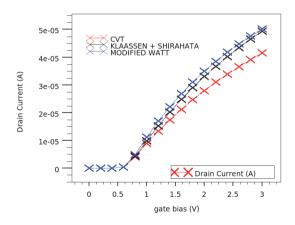

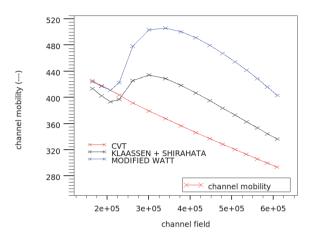

| Figure 4.20. Drain current of a MOSFET. Comparison for CVT, SHIRAHATA and                        |     |

| WATT mobility models                                                                             | 111 |

| Figure 4.21. Mobility in the channel: comparison of CVT, SHIRAHATA and                           |     |

| WATT mobility models                                                                             | 112 |

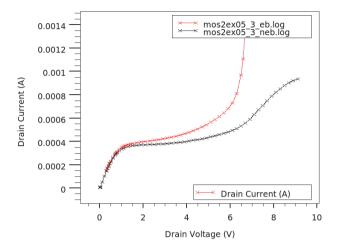

| Figure 4.22. Comparison of energy balance and non-isothermal energy balance                      |     |

| models                                                                                           |     |

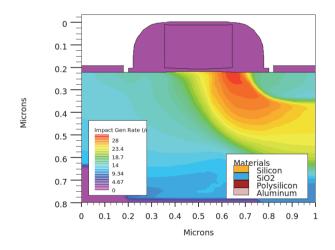

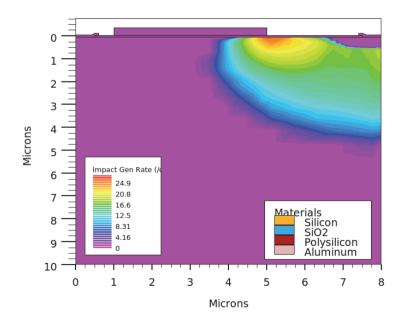

| Figure 4.23. Impact ionization rate due to nonlocal impact ionization effects                    | 113 |

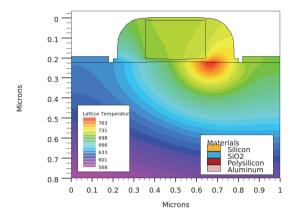

| Figure 4.24. Lattice temperature distribution in the device                                      | 114 |

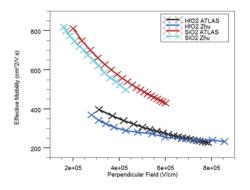

| Figure 4.25. Effective mobility vs. perpendicular field for HfO2 and SiO2 gate                   |     |

| dielectrics due to remote phonon scattering. Data used for comparison                            |     |

| purposes are after W. Zhu and T. Ma, Temperature Dependence                                      |     |

| of Channel Mobility in HfO2-Gated NMOSFETs, IEEE Elec. Dev. Lett.,                               |     |

| Vol. 25, pp. 89–91, 2004                                                                         | 115 |

| Figure 4.26. Effective mobility vs. perpendicular field for HfO <sub>2</sub> gate dielectric due |     |

| to remote Coulomb scattering. Data used for comparison purposes are                              |     |

| after H. Tanimoto et al., Modeling of Electron Mobility Degradation for                          |     |

| HfSiON MISFETs, Proc. of SISPAD, pp. 47-50, 2006                                                 |     |

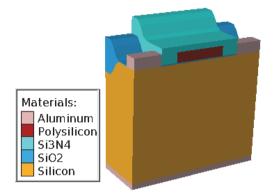

| Figure 4.27. DevEdit3D generated MOSFET structure                                                |     |

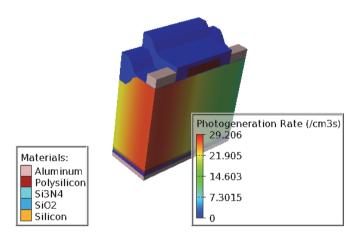

| Figure 4.28. Photo generation rate in the device                                                 |     |

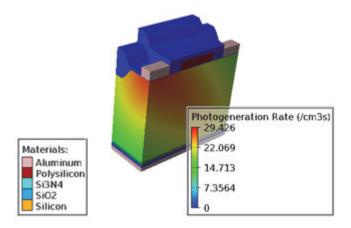

| Figure 4.29. Photo generation rate in the device                                                 |     |

| Figure 4.30. Potential distribution in the device                                                |     |

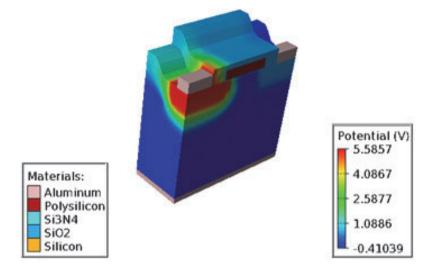

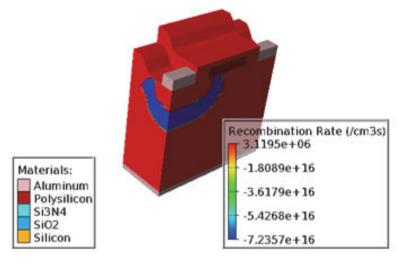

| Figure 4.31. Recombination rate in the device                                                    | 121 |

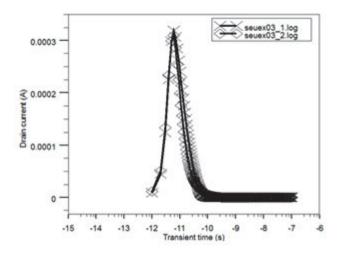

| Figure 4.32. Drain transient current characteristics corresponding to the different              |     |

| SEU conditions                                                                                   | 122 |

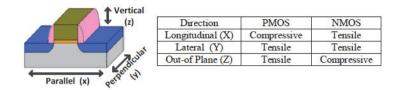

| Figure 5.1. Beneficial stress orientations for (a) PMOS and (b) NMOS transistors.                |     |

| The colors corresponding to longitudinal, transverse, and vertical                               |     |

| directions are purple, orange, and blue. Arrows pointing inward (outward)                        |     |

| indicate compressive (tensile) stress. After S. K. Marella, Performance                          |     |

| variations due to layout-dependent stress in VLSI circuits, PhD Thesis,                          |     |

| University of Minnesota, 2015                                                                    | 124 |

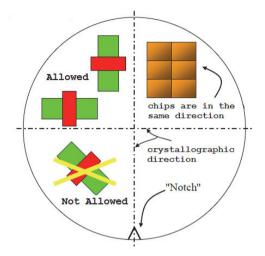

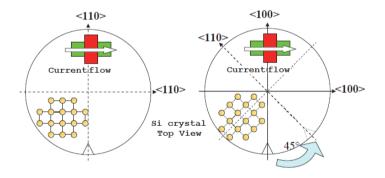

| Figure 5.2a. Representative substrate and its notch which serves as a reference to              |

|-------------------------------------------------------------------------------------------------|

| positioning on the chip (right) and the direction of current in the devices                     |

| (left)                                                                                          |

| Figure 5.2b. Schematic representation of types of substrate (001) used in 65nm                  |

| technology node. Orientation $(110)$ (left) and Orientation $(100)$ (right)                     |

| Figure 5.2c. 3-Dimensional representation of transistors with a substrate surface               |

| (100). In the case of left with a $\langle 110 \rangle$ orientation and plane (110) and in      |

| the case of right with a $(100)$ orientation and the sidewalls $(100)$                          |

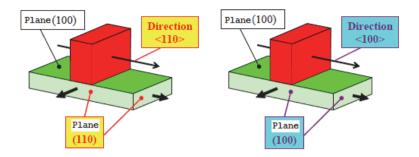

| Figure 5.3. $I_{ON}$ - $I_{OFF}$ characteristics of p-MOS devices (W = 1 $\mu$ m) undergone the |

| same manufacturing process but have two different current orientation                           |

| (110) and (100)                                                                                 |

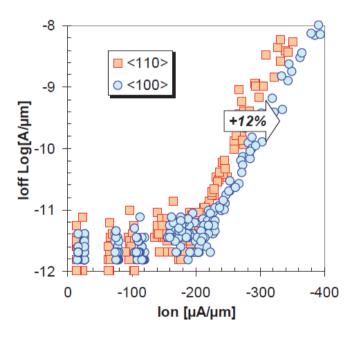

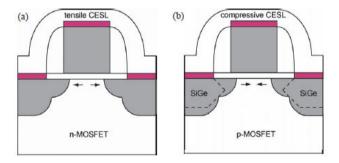

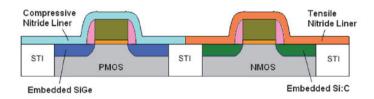

| Figure 5.4. Schematic demonstration of strained silicon schemes for                             |

| (a) n-MOSFETs and (b) p-MOSFETs                                                                 |

| Figure 5.5. Desired stress types for CMOS transistors                                           |

| Figure 5.6. Mechanical stress sources in CMOS transistors                                       |

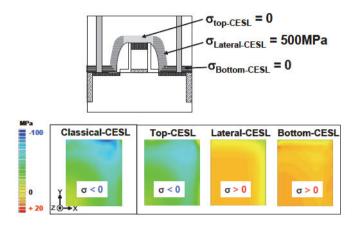

| Figure 5.7. Stress distribution schematic representation of the 3 zones (top-CESL,              |

| lateral-CESL, bottom-CESL) making up of the whole CESL. After V.                                |

| Fiori, How do Mechanics and Thermo mechanics affect microelectronic                             |

| products: Some residual stress and strain effects, investigations and                           |

| industrial management, PhD Thesis, L'institut national des sciences                             |

| appliquées de Lyon, 2010                                                                        |

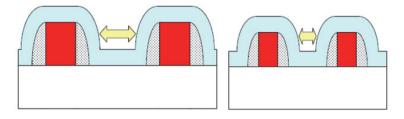

| Figure 5.8. Schematic representation of the problem of reduced dimensions for the               |

| CESL, left for a 65nm and right for 45nm technology node                                        |

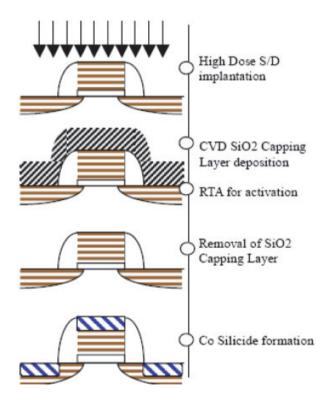

| Figure 5.9. Typical process steps used in stress memorization technique                         |

| Figure 5.10. Ion–IoFF characteristics of transistors for same process for reference             |

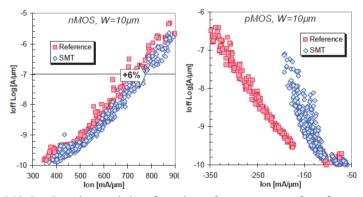

| and the SMT (left n-MOS) and right (p-MOS)                                                      |

| Figure 5.11. Stress distribution simulation using one-step and stress history models 137        |

| Figure 5.12. Formation of nitride stressor with one-layer model                                 |

| Figure 5.12. Formation of multi-layer stressor with one tayer model                             |

| Figure 5.14. 2D and 3D visualization of simulation results (screenshots)                        |

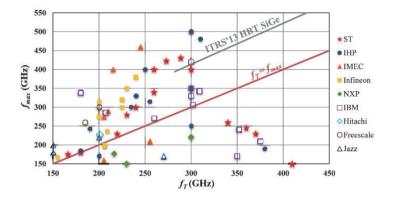

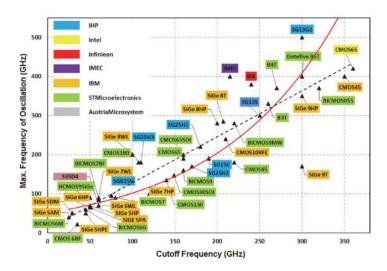

| Figure 6.1. State-of-the-art performance of the maximum frequency of oscillation,               |

| $f_{\text{max}}$ as a function cutoff frequency, $f_T$ of SiGe heterojunction bipolar           |

| transistors from major industrial manufacturers and research institutes                         |

| during 2002–2013. After M. Deng, Contribution a la caracterisation et la                        |

| modélisation jusqu'à 325 GHz de transistors HBT des technologies                                |

| BiCMOS, PhD Thesis, Universite de Lille, 2014                                                   |

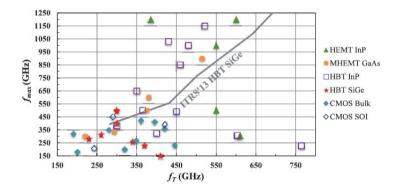

| Figure 6.2. State-of-the-art performance of the maximum frequency of oscillation,               |

| $f_{\text{max}}$ as a function cutoff frequency, $f_T$ for silicon and III–V transistors        |

| during 2004–2012. After M. Deng, Contribution a la caracterisation et la                        |

| modélisation jusqu'à 325 GHz de transistors HBT des technologies                                |

| BiCMOS, PhD Thesis, Universite de Lille, 2014                                                   |

| Dictation, Fild Thesis, Universite de Lille, 2014                                               |

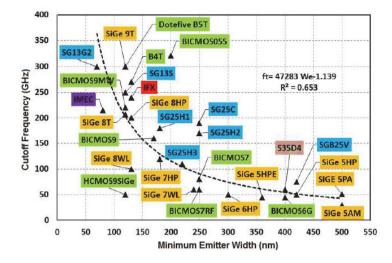

| Figure 6.3. Evolution in enhancement in the characteristic frequencies depending<br>on different technology nodes from foundries and research institutes.<br>After A. Serhan, Conception et réalisation de fonctions millimétriques en |       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| technologie BiCMOS 55nm, PhD Thesis, Universite Grenoble, 2015                                                                                                                                                                         | 143   |

| Figure 6.4. Evolution of the transition frequency as a function of the emitter width.                                                                                                                                                  |       |

| After A. Serhan, Conception et réalisation de fonctions millimétriques en                                                                                                                                                              |       |

| technologie BiCMOS 55nm, PhD Thesis, Universite Grenoble, 2015                                                                                                                                                                         | 146   |

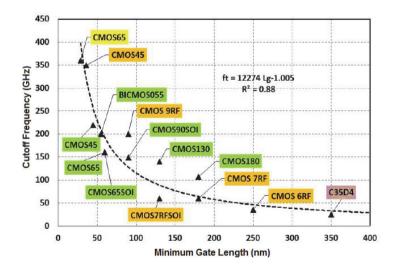

| Figure 6.5. Evolution of the transition frequency as a function of the width and                                                                                                                                                       |       |

| minimum gate length. After A. Serhan, Conception et réalisation de                                                                                                                                                                     |       |

| fonctions millimétriques en technologie BiCMOS 55nm, PhD Thesis,                                                                                                                                                                       |       |

| Universite Grenoble, 2015                                                                                                                                                                                                              | 146   |

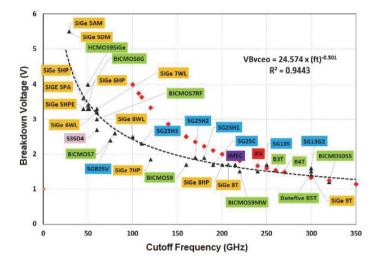

| Figure 6.6. Breakdown voltage as a function of the transition frequency of SiGe                                                                                                                                                        |       |

| bipolar transistors in advanced technologies. After A. Serhan, Conception                                                                                                                                                              |       |

| et réalisation de fonctions millimétriques en technologie BiCMOS 55nm,                                                                                                                                                                 |       |

| PhD Thesis, Universite Grenoble, 2015                                                                                                                                                                                                  | 147   |

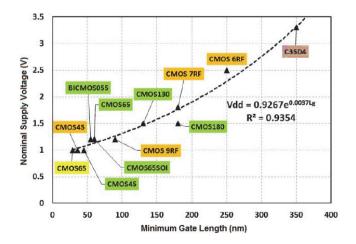

| Figure 6.7. Evolution of the nominal supply voltage $V_{dd}$ depending on the gate                                                                                                                                                     |       |

| width and minimum gate length for CMOS RF technologies. After A.                                                                                                                                                                       |       |

| Serhan, Conception et réalisation de fonctions millimétriques en                                                                                                                                                                       |       |

| technologie BiCMOS 55nm, PhD Thesis, Universite Grenoble, 2015                                                                                                                                                                         |       |

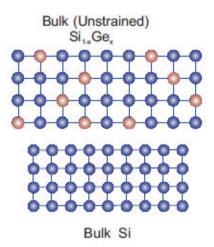

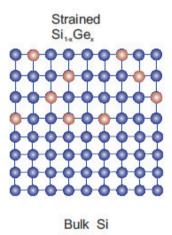

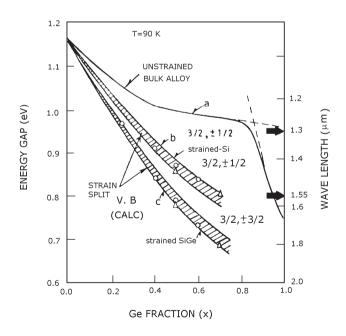

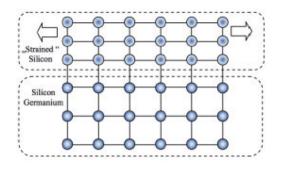

| Figure 6.8a. Bulk silicon and unstrained Si <sub>1-x</sub> Ge <sub>x</sub>                                                                                                                                                             | 150   |

| Figure 6.8b. Strained Si <sub>1-x</sub> Ge <sub>x</sub> : When the SiGe layer is thin, SiGe is                                                                                                                                         |       |

| commensurately deposited on the silicon substrate and under compressive                                                                                                                                                                |       |

| strain, with the in-plane lattice constant the same for both materials                                                                                                                                                                 | 150   |

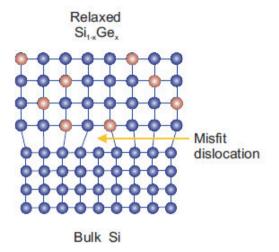

| Figure 6.8c. Relaxed $Si_{1-x}Ge_x$ : When the SiGe layer is thick, SiGe is relaxed by                                                                                                                                                 |       |

| misfit dislocations at the SiGe/Si interface                                                                                                                                                                                           | 151   |

| Figure 6.9. Bandgap as a function of Ge content for strained and unstrained                                                                                                                                                            |       |

| Si <sub>1-x</sub> Ge <sub>x</sub>                                                                                                                                                                                                      |       |

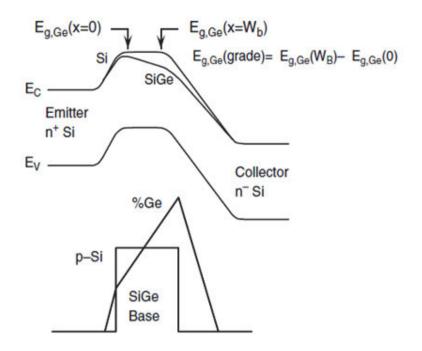

| Figure 6.10. Energy band diagram for a graded base SiGe HBT and a Si BJT                                                                                                                                                               | 153   |

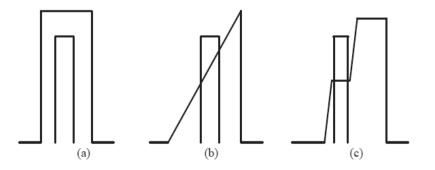

| Figure 6.11. Schematic of (a) Box-in-Box, (b) Graded, and (c) Modified Graded                                                                                                                                                          |       |

| base layer designs                                                                                                                                                                                                                     |       |

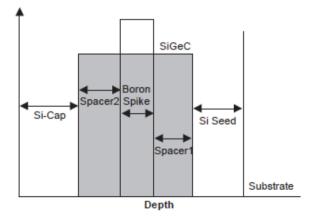

| Figure 6.12. Schematic of typical HBT base layer                                                                                                                                                                                       | 155   |

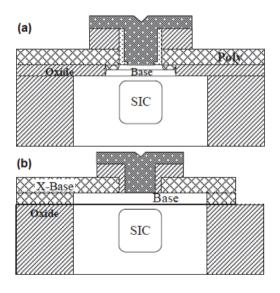

| Figure 6.13. Schematic cross section showing a basic (a) SEG base HBT and                                                                                                                                                              |       |

| (b) NSEG base HBT. After E. Haralson, Device design and process                                                                                                                                                                        |       |

| integration for SiGeC and Si/SOI bipolar transistors, PhD Thesis, Royal                                                                                                                                                                | 1.5.6 |

| Institute of Technology, 2004                                                                                                                                                                                                          | 156   |

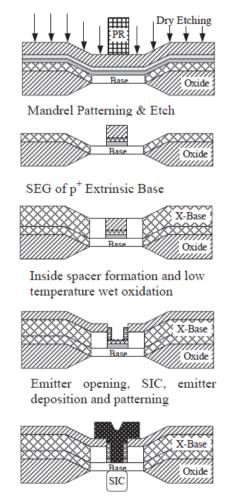

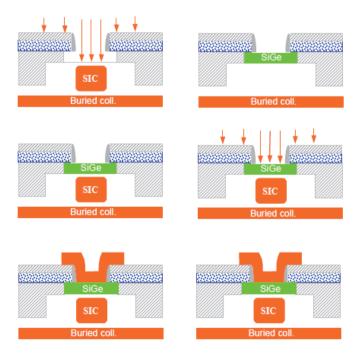

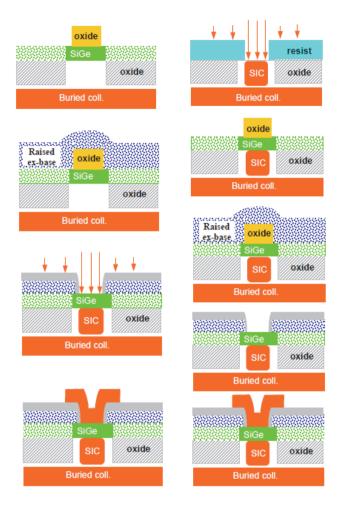

| Figure 6.14. Schematic cross sections of the SiGeC-HBT showing the raised                                                                                                                                                              |       |

| extrinsic base design. After E. Haralson, Device design and process                                                                                                                                                                    |       |

| integration for SiGeC and Si/SOI bipolar transistors, PhD Thesis, Royal                                                                                                                                                                | 1.50  |

| Institute of Technology, 2004                                                                                                                                                                                                          | 128   |

| Figure 6.15. SIC integration possibilities in a SEG base HBT design. After                                                                                                                                                             |       |

| E. Haralson, Device design and process integration for SiGeC and Si/SOI                                                                                                                                                                | 150   |

| bipolar transistors, PhD Thesis, Royal Institute of Technology, 2004                                                                                                                                                                   | 139   |

| Figure 6.16. SIC integration possibilities in a NSEG base HBT design. After                        |

|----------------------------------------------------------------------------------------------------|

| E. Haralson, Device design and process integration for SiGeC and Si/SOI                            |

| bipolar transistors, PhD Thesis, Royal Institute of Technology, 2004 160                           |

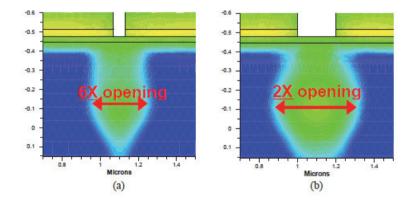

| Figure 6.17. Monte Carlo simulations comparing lateral straggle for different                      |

| emitter widths, (a) 0.05µm and (b) 0.2µm. After E. Haralson, Device                                |

| design and process integration for SiGeC and Si/SOI bipolar transistors,                           |

| PhD Thesis, Royal Institute of Technology, 2004                                                    |

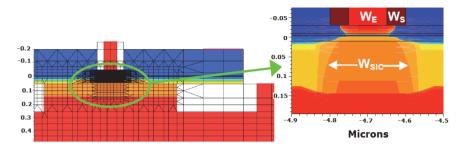

| Figure 6.18. Definition of the lateral device dimensions analyzed. After                           |

| E. Haralson, Device design and process integration for SiGeC and Si/SOI                            |

| bipolar transistors, PhD Thesis, Royal Institute of Technology, 2004                               |

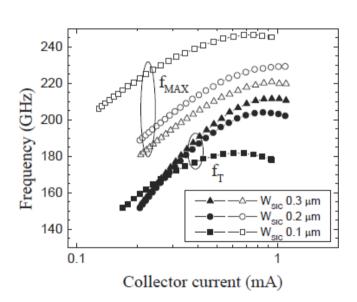

| Figure 6.19. $f_T$ and $f_{\text{max}}$ vs. Ic for different SIC widths. After E. Haralson, Device |

| design and process integration for SiGeC and Si/SOI bipolar transistors,                           |

| PhD Thesis, Royal Institute of Technology, 2004                                                    |

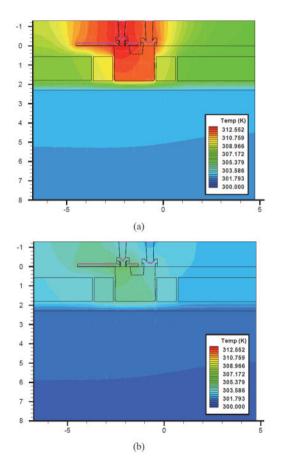

| Figure 6.20. 2D cross-sections showing the thermal contours for two different                      |

| boundary conditions at via surface. (a) Adiabatic and (b) Thermal                                  |

| resistance. After E. Haralson, Device design and process integration for                           |

| SiGeC and Si/SOI bipolar transistors, PhD Thesis, Royal Institute of                               |

| Technology, 2004                                                                                   |

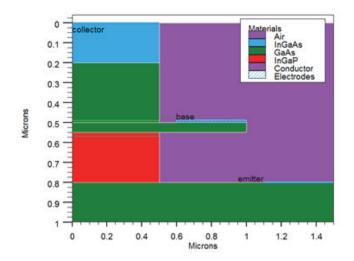

| Figure 6.21. The structure of collector-up InGaP/GaAs HBT with partially etched                    |

| extrinsic emitter                                                                                  |

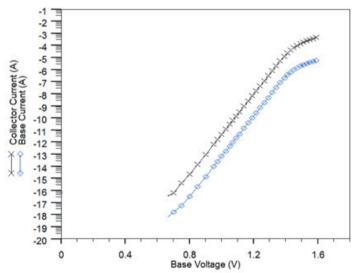

| Figure 6.22. Gummel-Poon characteristics for the extrinsic emitter completely                      |

| etched collector-up InGaP/GaAs HBT                                                                 |

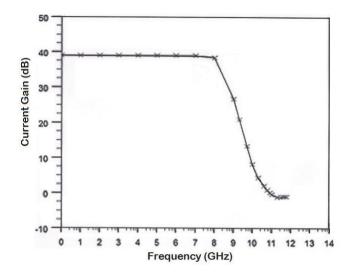

| Figure 6.23. AC characteristics of extrinsic emitter etched collector-up                           |

| InGaP/GaAs HBT                                                                                     |

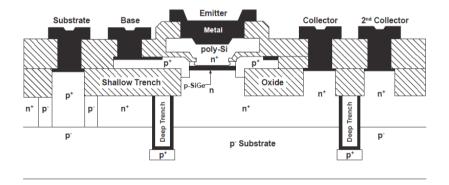

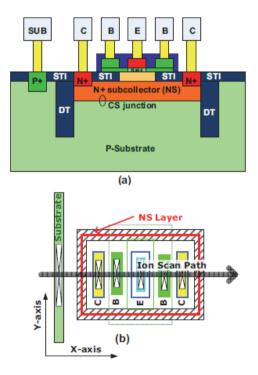

| Figure 6.24. Schematic device cross section of a first-generation SiGe HBT. After                  |

| M. Varadharajaperumal, 3D simulation of SEU in SiGe HBTs and                                       |

| radiation hardening by design, PhD Thesis, Auburn University, 2010                                 |

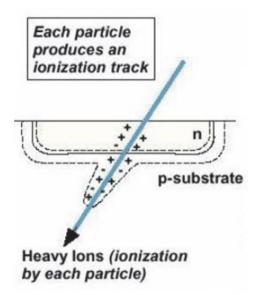

| Figure 6.25. Illustration of SEU in a pn junction                                                  |

| Figure 6.25. Industration of SEO in a prijunction                                                  |

| , ., .,                                                                                            |

| HBT (not to scale). After M. Varadharajaperumal, 3D simulation of SEU                              |

| in SiGe HBTs and radiation hardening by design, PhD Thesis, Auburn                                 |

| University, 2010                                                                                   |

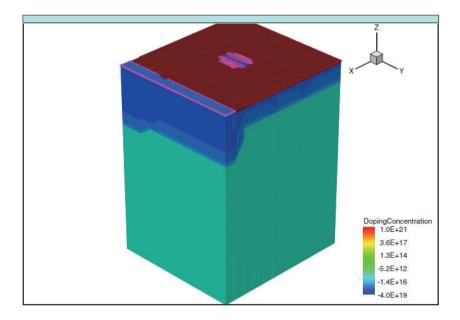

| Figure 6.27. 3D view of the 8HP regular HBT. Color indicates doping profile. After                 |

| M. Varadharajaperumal, 3D simulation of SEU in SiGe HBTs and                                       |

| radiation hardening by design, PhD Thesis, Auburn University, 2010                                 |

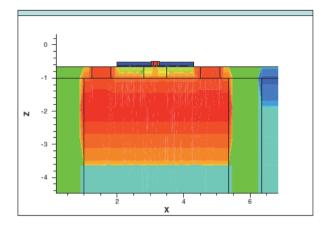

| Figure 6.28. 2DView of the 8HP regular HBT (cut made at the center of the                          |

| emitter). Color indicates doping profile. After M. Varadharajaperumal, 3D                          |

| simulation of SEU in SiGe HBTs and radiation hardening by design, PhD                              |

| Thesis, Auburn University, 2010                                                                    |

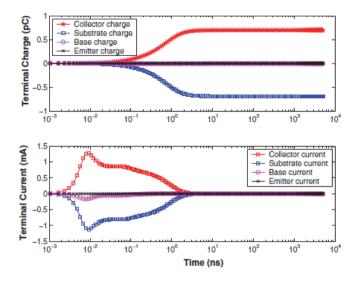

| Figure 6.29. Terminal current/charge for an ion strike at emitter center for the                   |

| 0.5×10 µm <sup>2</sup> 5HP HBT. After M. Varadharajaperumal, 3D simulation of                      |

| SEU in SiGe HBTs and radiation hardening by design, PhD Thesis, Auburn University, 2010                                                                                                                                                                                                                                                                                                                                                                               | 177   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

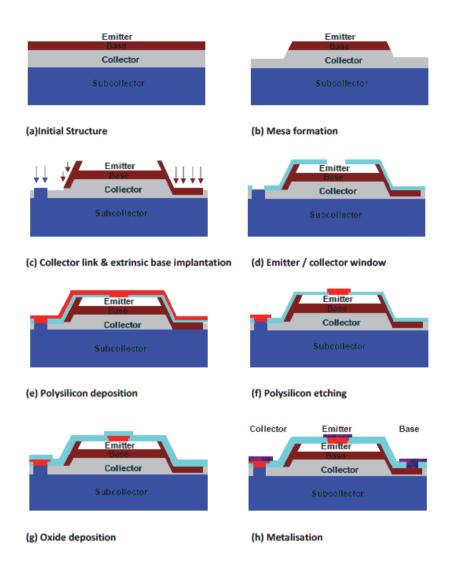

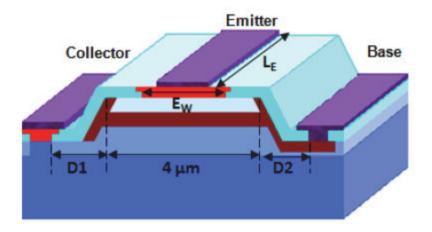

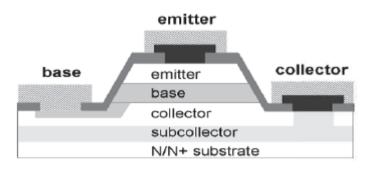

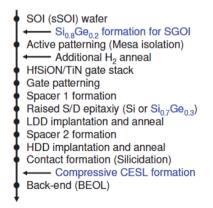

| Figure 7.1. Simplified process flow, Si BJTs, SiGe HBTs and strained-Si HBTs were fabricated using the same process flow. After M. Fjer, Strained Si heterojunction bipolar transistors, PhD Thesis, Newcastle University, 2011                                                                                                                                                                                                                                       |       |

| Figure 7.2. Schematic diagram illustrating different parameters design space. After                                                                                                                                                                                                                                                                                                                                                                                   | 102   |

| M. Fjer, Strained Si heterojunction bipolar transistors, PhD Thesis,<br>Newcastle University, 2011                                                                                                                                                                                                                                                                                                                                                                    | . 183 |

| Figure 7.3. Schematic of the final strained Si HBT structure. After M. Fjer, Strained                                                                                                                                                                                                                                                                                                                                                                                 |       |

| Si heterojunction bipolar transistors, PhD Thesis, Newcastle University, 2011                                                                                                                                                                                                                                                                                                                                                                                         | . 183 |

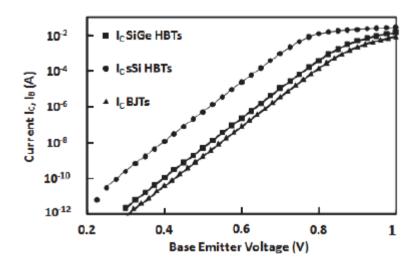

| Figure 7.4. Collector current for strained-Si HBTs, SiGe HBTs and Si BJTs @                                                                                                                                                                                                                                                                                                                                                                                           |       |

| $V_{BC}$ = 0 V. $W_E$ = 1 $\mu$ m and $L_E$ = 10 $\mu$ m. After M. Fjer, Strained Si                                                                                                                                                                                                                                                                                                                                                                                  |       |

| heterojunction bipolar transistors, PhD Thesis, Newcastle University, 2011                                                                                                                                                                                                                                                                                                                                                                                            | . 184 |

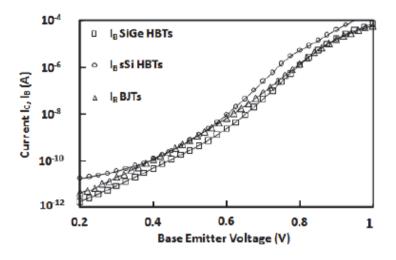

| Figure 7.5. Base current for strained-Si HBTs, SiGe HBTs and Si BJTs @ $V_{BC} = 0$                                                                                                                                                                                                                                                                                                                                                                                   |       |

| V. $W_E = 1 \mu m$ and $L_E = 10 \mu m$ . After M. Fjer, Strained Si heterojunction                                                                                                                                                                                                                                                                                                                                                                                   |       |

| bipolar transistors, PhD Thesis, Newcastle University, 2011                                                                                                                                                                                                                                                                                                                                                                                                           | 185   |

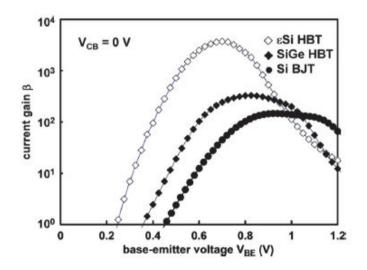

| Figure 7.6. Current gain $\beta$ vs. BE voltage V <sub>BE</sub> . $\beta$ is increased by more than one order of magnitude in the strained-Si HBT, as compared with the SiGe HBT and the Si BJT. W <sub>E</sub> = 1 $\mu$ m and L <sub>E</sub> = 10 $\mu$ m. After M. Fjer, Strained Si heterojunction bipolar transistors, PhD Thesis, Newcastle University, 2011                                                                                                    | . 185 |

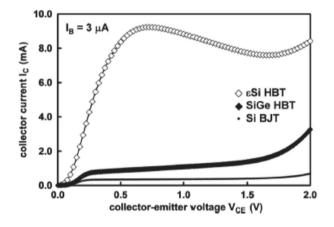

| Figure 7.7. Comparison of collector current I <sub>C</sub> vs. collector–emitter voltage V <sub>CE</sub> characteristics for strained-Si HBTs, SiGe HBTs, and Si BJTs at I <sub>B</sub> = $3\mu$ A. Self-heating is observed for strained-Si HBTs, but no SHEs are observed on Si BJTs and SiGe HBTs. W <sub>E</sub> = $1\mu$ m and L <sub>E</sub> = $10\mu$ m. After M. Fjer, Strained Si heterojunction bipolar transistors, PhD Thesis, Newcastle University, 2011 |       |

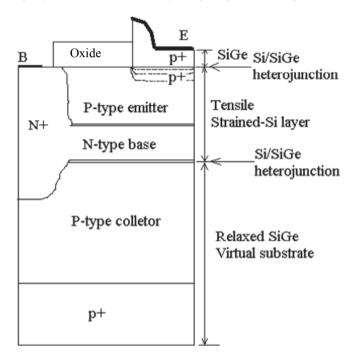

| Figure 7.8. 2D cross-section of the schematic of the simulated virtual substrate PNP<br>HBT device with strained-Si/SiGe (relaxed) hetero-interface at the base–<br>collector junction and emitter bulk contact. After C. Mukherjee, Strain<br>engineering in heterojunction bipolar transistors, MTech Thesis, IIT<br>Kharagpur, 2010                                                                                                                                |       |

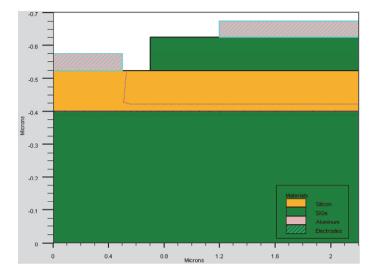

| Figure 7.9. Simulated PNP strained-Si on virtual substrate HBT structure. After C.                                                                                                                                                                                                                                                                                                                                                                                    |       |

| Mukherjee, Strain engineering in heterojunction bipolar transistors,<br>MTech Thesis, IIT Kharagpur, 2010                                                                                                                                                                                                                                                                                                                                                             | . 191 |

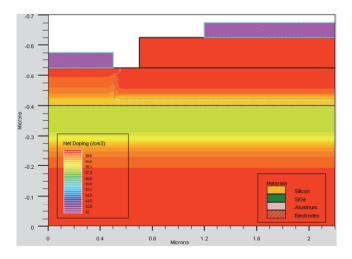

| Figure 7.10a. Doping contours of simulated PNP strained-Si on virtual substrate                                                                                                                                                                                                                                                                                                                                                                                       |       |

| HBT. After C. Mukherjee, Strain engineering in heterojunction bipolar transistors, MTech Thesis, IIT Kharagpur, 2010                                                                                                                                                                                                                                                                                                                                                  | . 191 |

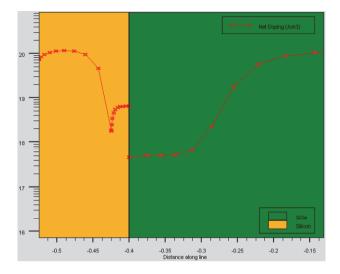

| Figure 7.10b. Doping profile of simulated PNP strained-Si on virtual substrate<br>HBT. After C. Mukherjee, Strain engineering in heterojunction bipolar       | <b>1</b> 7     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| transistors, MTech Thesis, IIT Kharagpur, 2010                                                                                                                | 12             |

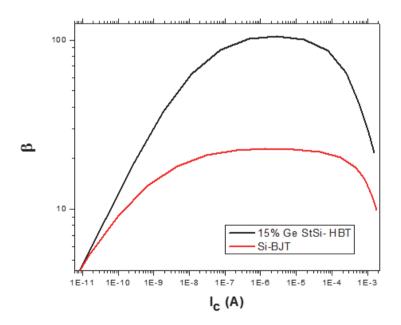

| virtual substrate HBT with that of the identical Si-BJT. After                                                                                                |                |

| C. Mukherjee, Strain engineering in heterojunction bipolar transistors,                                                                                       |                |

| MTech Thesis, IIT Kharagpur, 2010                                                                                                                             | 93             |

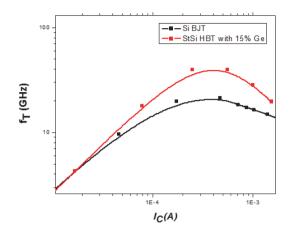

| Figure 7.12. Cutoff frequency comparison between the simulated PNP strained-Si                                                                                | -              |

| on virtual substrate HBT with that of the identical Si-BJT. After                                                                                             |                |

| C. Mukherjee, Strain engineering in heterojunction bipolar transistors,                                                                                       |                |

| MTech Thesis, IIT Kharagpur, 2010                                                                                                                             | <del>)</del> 4 |

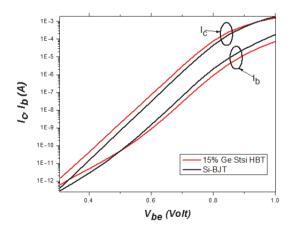

| Figure 7.13. Gummel plot comparison between the simulated PNP strained-Si on                                                                                  |                |

| virtual substrate HBT with that of the identical Si-BJT. After                                                                                                |                |

| C. Mukherjee, Strain engineering in heterojunction bipolar transistors,                                                                                       |                |

| MTech Thesis, IIT Kharagpur, 2010                                                                                                                             | <del>)</del> 4 |

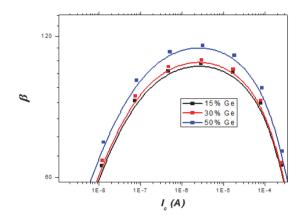

| Figure 7.14. Current gain variation with increasing Ge fractions (15%, 30%, 50%)                                                                              |                |

| for the simulated PNP strained-Si on virtual substrate HBT. After                                                                                             |                |

| C. Mukherjee, Strain engineering in heterojunction bipolar transistors,                                                                                       |                |

| MTech Thesis, IIT Kharagpur, 2010                                                                                                                             | <del>)</del> 5 |

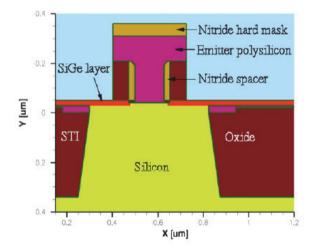

| Figure 7.15. The final device schematic after the process simulation. After M. Al-                                                                            |                |

| Sadi, TCAD based SiGe HBT advanced architecture exploration, PhD                                                                                              |                |

| Thesis, Universite Bordeaux I, 2011 19                                                                                                                        | <del>)</del> 6 |

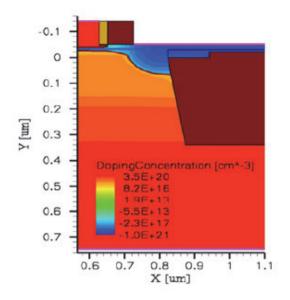

| Figure 7.16. Cross-section of the one half of the device used for device simulation.                                                                          |                |

| After M. Al-Sadi, TCAD based SiGe HBT advanced architecture                                                                                                   |                |

| exploration, PhD Thesis, Universite Bordeaux I, 2011                                                                                                          | <del>)</del> 7 |

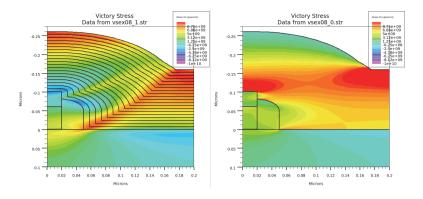

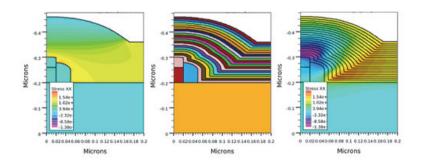

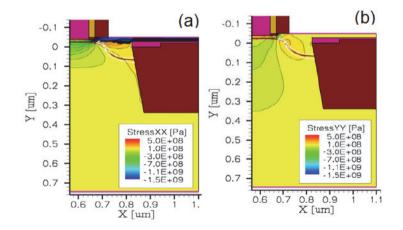

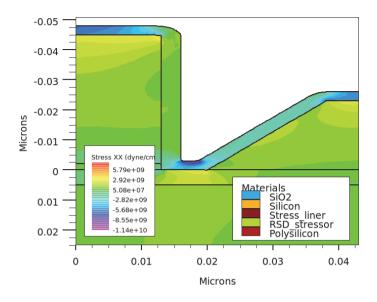

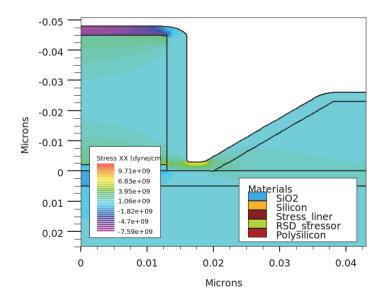

| Figure 7.17. Cross section of the one half the device region of interest, the                                                                                 |                |

| isocontour lines represent the stress Sxx (a) induced in the x-direction and                                                                                  |                |

| Syy (b) induced in the y-direction of the structure. After M. Al-Sadi,                                                                                        |                |

| TCAD based SiGe HBT advanced architecture exploration, PhD Thesis,                                                                                            |                |

| Universite Bordeaux I, 2011                                                                                                                                   | <del>)</del> 7 |

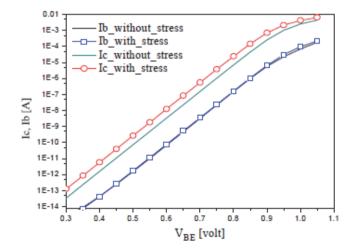

| Figure 7.18. Comparison of forward Gummel plots for both conventional BJT, and                                                                                |                |

| BJT with stress layer (Ge = 25%, $W_E$ = 130nm). After M. Al-Sadi, TCAD                                                                                       |                |

| based SiGe HBT advanced architecture exploration, PhD Thesis,                                                                                                 | 20             |

| Universite Bordeaux I, 2011                                                                                                                                   | <del>9</del> 8 |

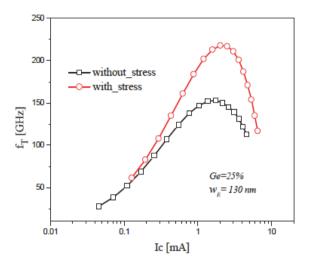

| Figure 7.19. Cutoff frequency as a function of collector current for both devices $(2 - 25\%)$ W = 120 $(2 - 25\%)$ M = 120 $(2 - 25\%)$ M = 120 $(2 - 25\%)$ |                |

| (Ge = 25%, $W_E$ = 130nm). After M. Al-Sadi, TCAD based SiGe HBT                                                                                              |                |

| advanced architecture exploration, PhD Thesis, Universite Bordeaux I,                                                                                         | 20             |

| 2011                                                                                                                                                          | 19             |

| Figure 7.20. Maximum oscillation frequency as a function of collector current for both devices (Ge = 25%, $W_E$ = 130nm). After M. Al-Sadi, TCAD based        |                |

| SiGe HBT advanced architecture exploration, PhD Thesis, Universite                                                                                            |                |

| Bordeaux I. 2011                                                                                                                                              | 20             |

| DUIQUUA 1, 2011                                                                                                                                               | 11             |

J

xx

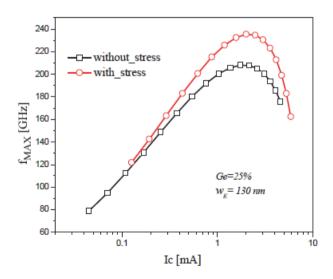

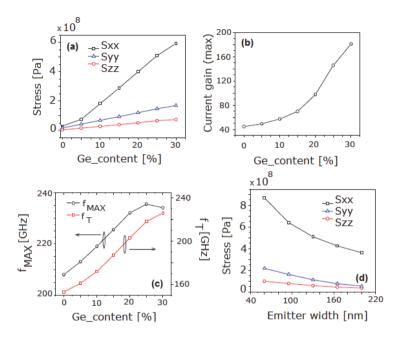

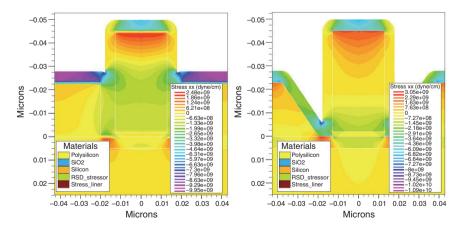

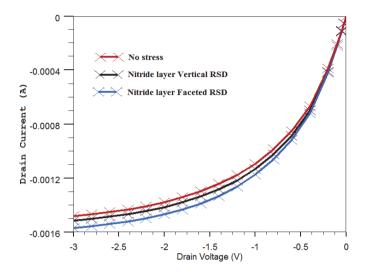

| Figure 7.21. (a) Variation of the stress values generated inside the device with Ge                          |

|--------------------------------------------------------------------------------------------------------------|

| content at the stress layer ( $W_E = 130$ nm), (b) variation of the maximum                                  |

| current gain with Ge content at the stress layer ( $W_E = 130$ nm),                                          |

| (c) variation of $f_T$ and $f_{max}$ with Ge content at the stress layer (W <sub>E</sub> =                   |

| 130nm), and (d) variation of the stress values generated inside the device                                   |

| with the device emitter width. After M. Al-Sadi, TCAD based SiGe HBT                                         |

| advanced architecture exploration, PhD Thesis, Universite Bordeaux I,                                        |

| 2011                                                                                                         |

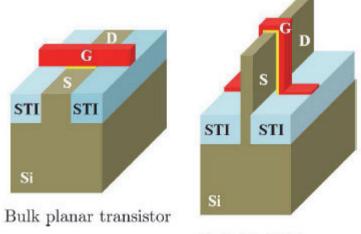

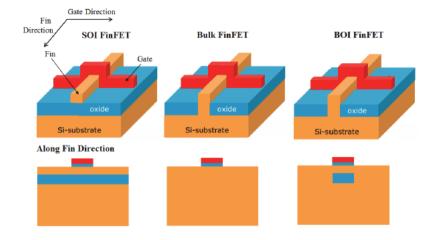

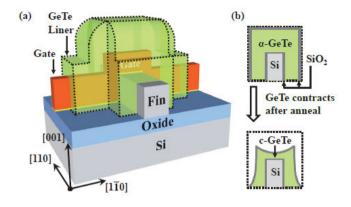

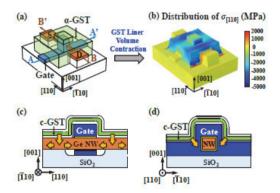

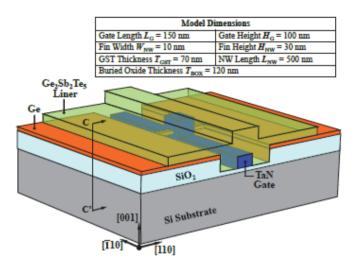

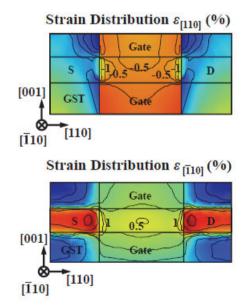

| Figure 8.1. Comparison of bulk planar transistor and bulk FinFET. The gate oxide                             |

| is shown in yellow regions                                                                                   |

| Figure 8.2. Possible substrate types of FinFET. After P. Feng, Design, modeling                              |

|                                                                                                              |

| and analysis of non-classical field effect transistors, PhD Thesis, Syracuse                                 |

| University, 2009                                                                                             |

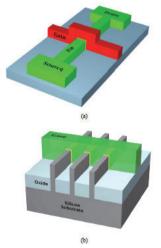

| Figure 8.3. (a) The structure of FinFETs. (b) Tri-gate technology by Intel where                             |

| multiple fins are connected together. After L. Han, Investigation of gate                                    |

| dielectric materials and dielectric/silicon interfaces for metal oxide                                       |

| semiconductor devices, PhD Thesis, University of Kentucky, 2015 206                                          |

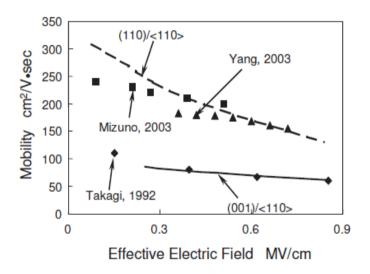

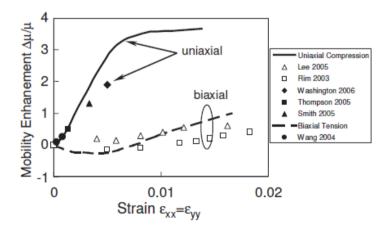

| Figure 8.4. Hole mobility vs. inversion charge density for relaxed silicon. Both                             |

| measurements and simulation show larger mobility on (110) device. After                                      |

| G. Sun, Strain effects on hole mobility of silicon and germanium P-type                                      |

| metal-oxide-semiconductor field-effect-transistors, PhD Thesis,                                              |

| University of Florida, 2007                                                                                  |

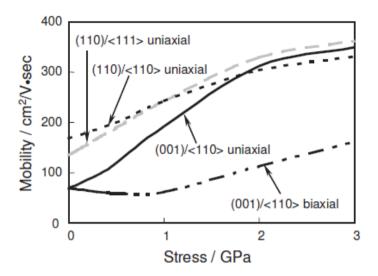

| Figure 8.5. Hole mobility vs. stress with inversion charge density $1 \times 10^{13}$ cm <sup>-2</sup> . The |

| enhancement factor is the highest for $(001)/(110)$ devices and lowest for                                   |

| (110)/(110) devices. At high stress (3 GPa), three uniaxial stress cases                                     |

|                                                                                                              |

| have similar hole mobility. After G. Sun, Strain effects on hole mobility                                    |

| of silicon and germanium P-type metal-oxide-semiconductor field-effect-                                      |

| transistors, PhD Thesis, University of Florida, 2007                                                         |

| Figure 8.6. Calculated strain induced hole mobility enhancement factor vs.                                   |

| experimental data for (001)-oriented p-MOSFET. After G. Sun, Strain                                          |

| effects on hole mobility of silicon and germanium P-type metal-oxide-                                        |

| semiconductor field-effect-transistors, PhD Thesis, University of Florida,                                   |

| 2007                                                                                                         |

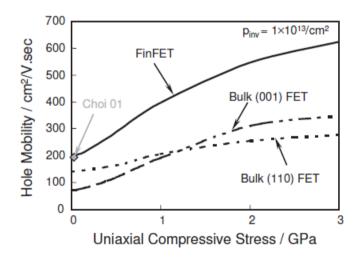

| Figure 8.7. Hole mobility of FinFETs under uniaxial stress compared with bulk                                |

| (110)-oriented devices at charge density $p = 1 \times 10^{13} \text{ cm}^{-2}$ . After G. Sun,              |

| Strain effects on hole mobility of silicon and germanium P-type metal-                                       |

| oxide-semiconductor field-effect-transistors, PhD Thesis, University of                                      |

| Florida, 2007                                                                                                |

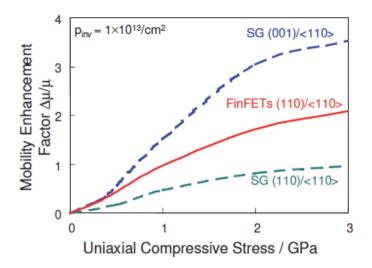

| Figure 8.8. Hole mobility enhancement factor of FinFETs under uniaxial                                       |

|                                                                                                              |

| compressive stress at charge density $p = 1 \times 10^{13} \text{ cm}^{-2}$ . After G. Sun, Strain           |

| effects on hole mobility of silicon and germanium P-type                                                     |

| metal-oxide-semiconductor field-effect-transistors, PhD Thesis,                                          |       |

|----------------------------------------------------------------------------------------------------------|-------|

| University of Florida, 2007                                                                              | . 212 |

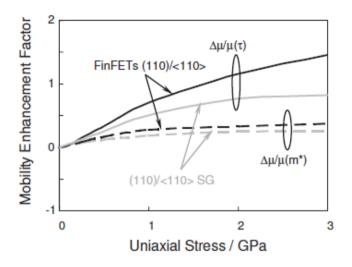

| Figure 8.9. Hole mobility gain contribution from effective mass and phonon                               |       |

| scattering suppression under uniaxial compression for $(110)/(110)$                                      |       |

| FinFETs compared with SG (110)/(110) p-MOSFETs at charge density                                         |       |

| $p = 1 \times 10^{13}$ cm <sup>-2</sup> . After G. Sun, Strain effects on hole mobility of silicon       |       |

| and germanium P-type metal-oxide-semiconductor field-effect-transistors,                                 |       |

| PhD Thesis, University of Florida, 2007                                                                  | . 213 |

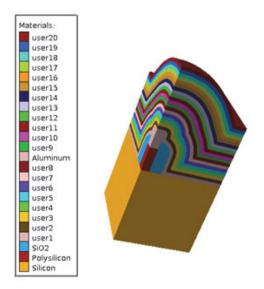

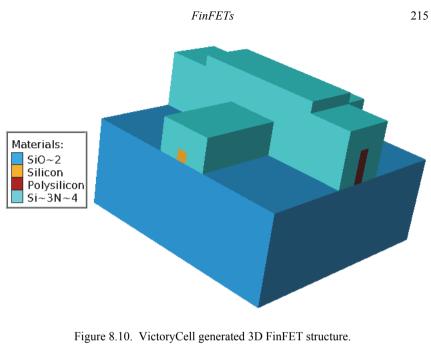

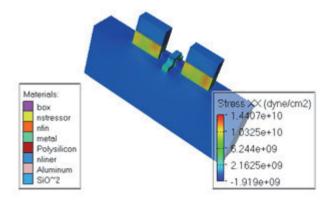

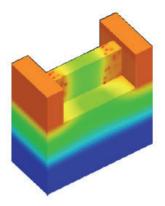

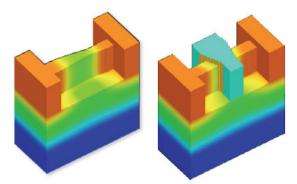

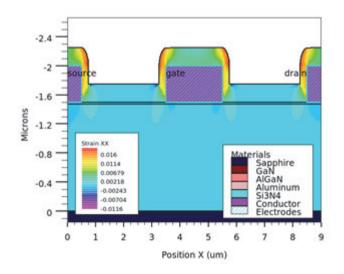

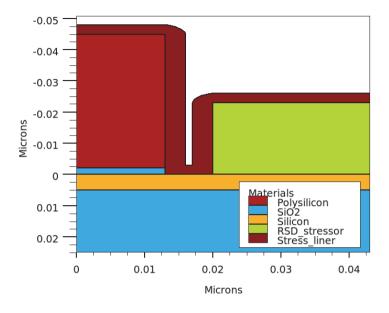

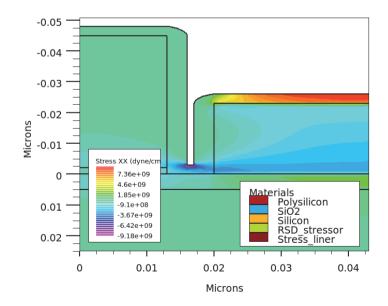

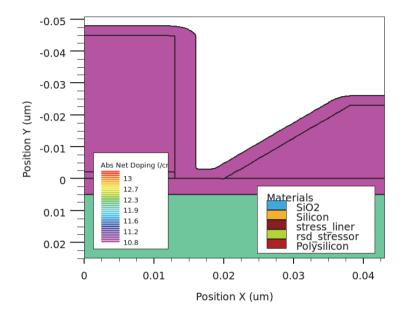

| Figure 8.10. VictoryCell generated 3D FinFET structure                                                   | . 215 |

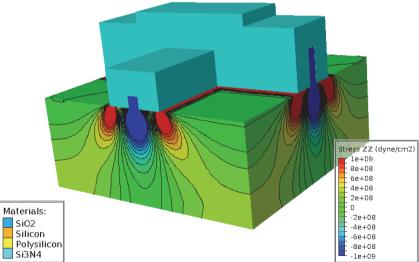

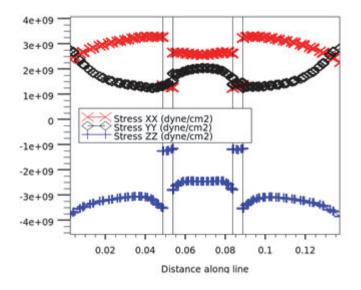

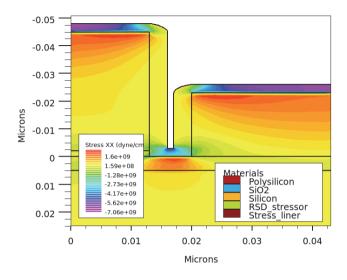

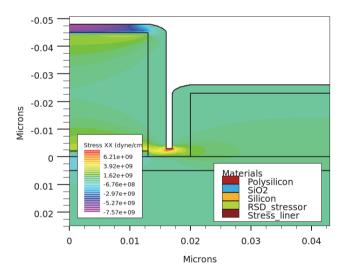

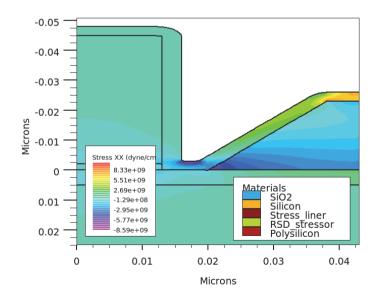

| Figure 8.11. VictoryStress generated stress transfer in the FinFET                                       | . 215 |

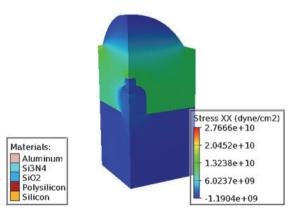

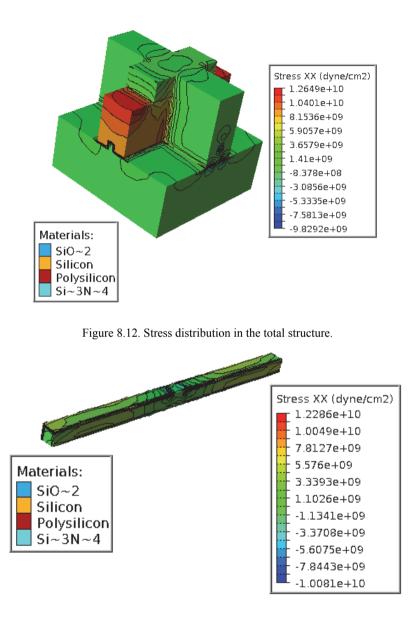

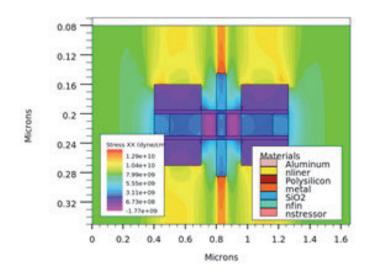

| Figure 8.12. Stress distribution in the total structure                                                  | . 216 |

| Figure 8.13. Stress distribution in the fin                                                              | . 216 |

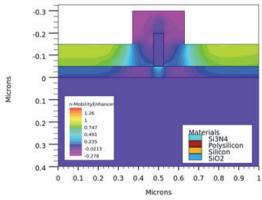

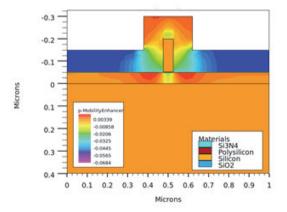

| Figure 8.14. 2D cut plane electron enhancement factor in FinFET                                          | . 217 |

| Figure 8.15. 2D cut plane hole enhancement factor in FinFET                                              | . 217 |

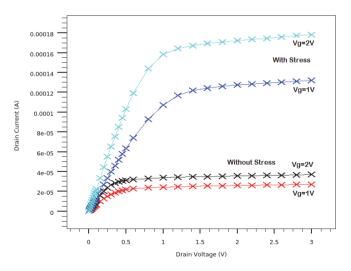

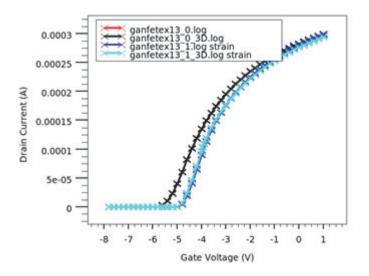

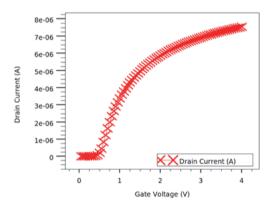

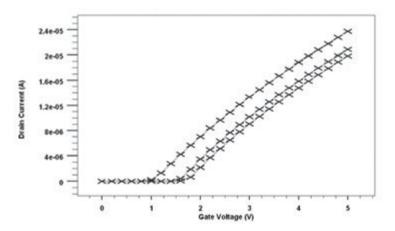

| Figure 8.16. Electrical characterization (I <sub>d</sub> - V <sub>g</sub> ) using device simulation tool |       |

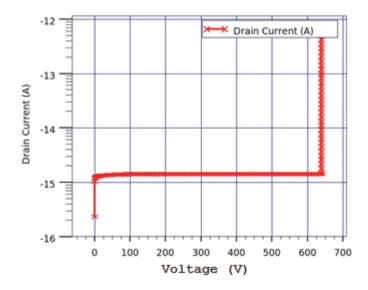

| VictoryDevice                                                                                            | . 218 |

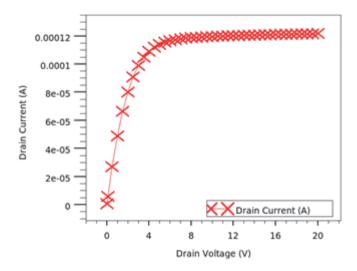

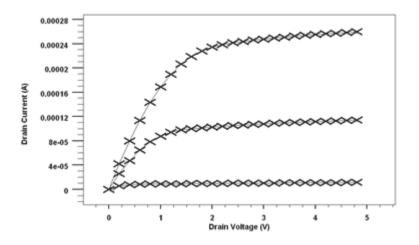

| Figure 8.17. Electrical characterization (I <sub>d</sub> - V <sub>d</sub> ) using device simulation tool |       |

| VictoryDevice                                                                                            | . 218 |

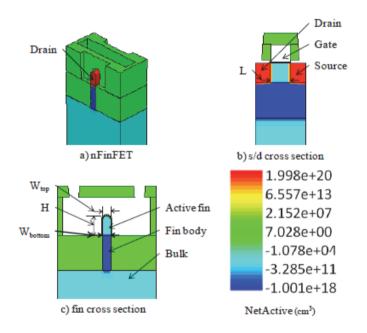

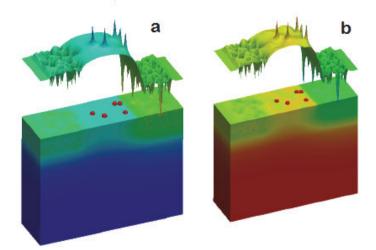

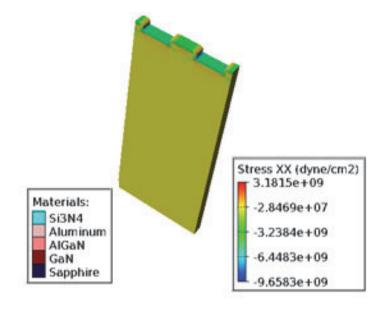

| Figure 8.18. The 3D view of n-FinFET device. Only BOX substrate and active area                          |       |

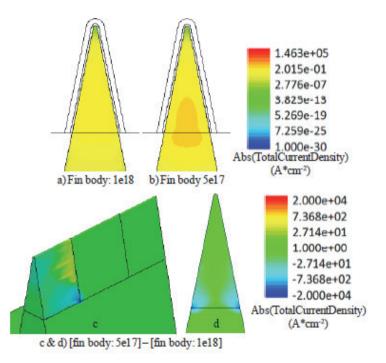

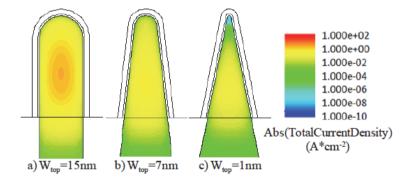

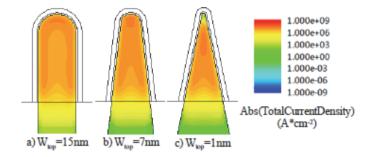

| of device with Sxx stress distribution is shown                                                          | . 221 |